#### Silicon General Purpose x5 NPN Transistor array in PDIP-14

Rev 1.1 20/10/17

#### Description

The SiS3046P consists of five general purpose silicon NPN transistors on a common monolithic substrate. Two of the transistors are internally connected to form a differentially-connected pair. The transistors are well suited to a wide variety of applications in low power systems in the DC through VHF range. They may be used as discrete transistors in conventional circuits however; in addition, they provide the very significant inherent integrated circuit advantages of close electrical and thermal matching. The SiS3046P is a direct electrical & mechanical replacement for the obsolete Intersil CA3046.

#### Features:

- Two matched transistors:

- V<sub>BE</sub> Match ±5mA

- I<sub>IO</sub> Match 2µA (Max).

- Low Noise Figure 3.2dB (Typ) at 1kHz

- Operation From DC to 120MHz

- Wide Operating Current Range

- Full Military Temperature Range.

#### **Ordering Information**

The following part suffixes apply:

SiS3046P - 14 Lead Plastic Dual-In-Line - RoHS compliant

#### Applications:

- Three Isolated Transistors and One Differentially Connected Transistor Pair for Low Power Applications at Frequencies from DC Through the VHF Range

- Custom Designed Differential Amplifiers

- Temperature Compensated Amplifiers.

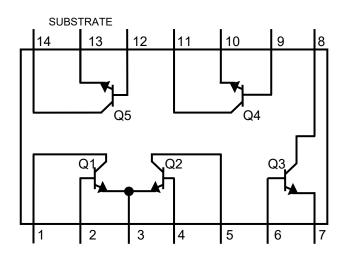

#### Schematic & Connection Diagram

#### **Absolute Maximum Ratings**

| PARAMETER                                      | SYMBOL           | VALUE      | UNIT |

|------------------------------------------------|------------------|------------|------|

| Collector-to-Emitter Voltage                   | V <sub>CEO</sub> | 15         | V    |

| Collector-to-Base Voltage                      | $V_{CBO}$        | 20         | V    |

| Collector-to-Substrate Voltage (Note 1)        | V <sub>CIO</sub> | 20         | V    |

| Emitter-to-Base Voltage                        | $V_{EBO}$        | 5          | V    |

| Collector Current                              | I <sub>C</sub>   | 50         | mA   |

| Maximum Power Dissipation (Any one transistor) | P <sub>D</sub>   | 300        | mW   |

| Operating Temperature Range                    | -                | -55 to 125 | °C   |

| Maximum Junction Temperature                   | T <sub>J</sub>   | 175        | °C   |

#### Rev 1.1 20/10/17

### DC Electrical Characteristics T<sub>A</sub> = 25°C unless otherwise stated

| PARAMETER                                                                           | SYMBOL                                                                                                                  | TEST CONDITIONS                            |                         | MIN                  | TYP                  | MAX | UNITS |   |   |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------|----------------------|----------------------|-----|-------|---|---|

| Collector to Base Breakdown Voltage                                                 | V <sub>(BR)CBO</sub>                                                                                                    | $I_{C} = 10\mu A, I_{E} = 0$               |                         | 20                   | 60                   | -   | V     |   |   |

| Collector to Emitter Breakdown Voltage                                              | V <sub>(BR)CEO</sub>                                                                                                    | $I_{\rm C} = 1 {\rm mA}, I_{\rm B} = 0$    |                         | 15                   | 24                   | -   | V     |   |   |

| Collector-to-Substrate Breakdown<br>Voltage                                         | V <sub>(BR)CIO</sub>                                                                                                    | I <sub>C</sub> = 10                        | μΑ, I <sub>CI</sub> = 0 | 20                   | 60                   | -   | V     |   |   |

| Emitter to Base Breakdown Voltage                                                   | V <sub>(BR)EBO</sub>                                                                                                    | I <sub>E</sub> = 10                        | $\mu$ A, $I_{C}$ = 0    | 5                    | 7                    | -   | V     |   |   |

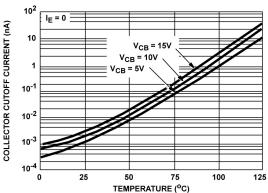

| Collector Cutoff Current                                                            | I <sub>CBO</sub>                                                                                                        | $V_{CB} = 1$                               | 0V, I <sub>E</sub> = 0  | -                    | 0.002                | 40  | nA    |   |   |

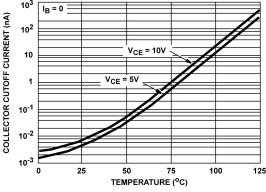

| Collector Cutoff Current (Figure 2)                                                 | I <sub>CEO</sub>                                                                                                        | V <sub>CE</sub> = 1                        | 0V, I <sub>B</sub> = 0  | -                    | FIG 2                | 0.5 | μA    |   |   |

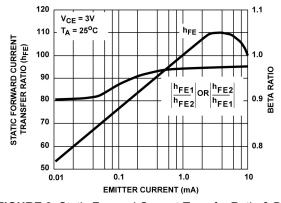

| Forward Current Transfer Ratio                                                      |                                                                                                                         |                                            | I <sub>C</sub> = 10mA   | -                    | 100                  | -   | -     |   |   |

| (Static Beta) (Note 3) (Figure 3)                                                   | h <sub>FE</sub>                                                                                                         | V <sub>CE</sub> =3V                        | $I_C = 1mA$             | 40                   | 100                  | -   | -     |   |   |

|                                                                                     |                                                                                                                         |                                            | $I_C = 10\mu A$         | -                    | 54                   | -   | -     |   |   |

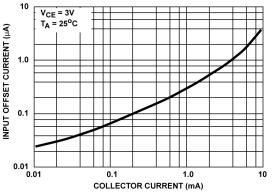

| Input Offset Current for Matched Pair Q1 and Q2. (Note 2) (Figure 4)                | I <sub>IO1</sub> - I <sub>IO2</sub>                                                                                     | V <sub>CE</sub> = 3\                       | /, I <sub>C</sub> = 1mA | -                    | 0.3                  | 2   | μA    |   |   |

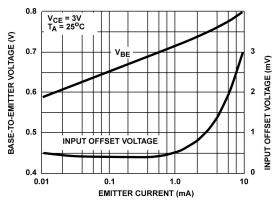

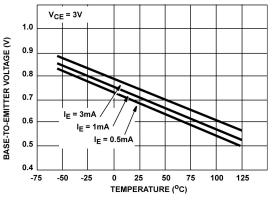

| Base-to-Emitter Voltage (Note 2)                                                    | \/                                                                                                                      | V <sub>BE</sub> V <sub>CE</sub> = 3V       | $I_E = 1mA$             | -                    | 0.715                | -   | V     |   |   |

| (Figure 5)                                                                          | V <sub>BE</sub>                                                                                                         | ▼ BE                                       | V BE                    | V <sub>CE</sub> - 3V | I <sub>E</sub> =10mA | -   | 0.800 | - | V |

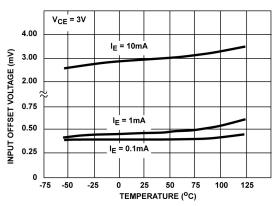

| Magnitude of Input Offset Voltage for Differential Pair (Note 2) (Figures 5, 7)     | V <sub>BE1</sub> - V <sub>BE2</sub>                                                                                     | V <sub>CE</sub> = 3\                       | /, I <sub>C</sub> = 1mA | -                    | 0.45                 | 5   | mV    |   |   |

| Magnitude of Input Offset Voltage for Isolated Transistors. (Note 2) (Figures 5, 7) | V <sub>BE3</sub> - V <sub>BE4</sub>  <br> V <sub>BE4</sub> - V <sub>BE5</sub>  <br> V <sub>BE5</sub> - V <sub>BE3</sub> | V <sub>CE</sub> = 3V, I <sub>C</sub> = 1mA |                         | -                    | 0.45                 | 5   | mV    |   |   |

| Temperature Coefficient of Base-to-<br>Emitter Voltage (Figure 6)                   | $\frac{\Delta V_{BE}}{\Delta T}$                                                                                        | V <sub>CE</sub> = 3V, I <sub>C</sub> = 1mA |                         | -                    | -1.9                 | -   | mV/°C |   |   |

| Collector-to-Emitter Saturation Voltage                                             | V <sub>CES</sub>                                                                                                        | $I_B = 1 \text{mA}$                        | , I <sub>C</sub> = 10mA | -                    | 0.23                 | -   | V     |   |   |

| Temperature Coefficient: Magnitude of Input Offset Voltage (Figure 7)               | ΔV <sub>IO</sub>  <br><u>ΔT</u>                                                                                         | V <sub>CE</sub> = 3\                       | /, I <sub>C</sub> = 1mA | -                    | 1.1                  | -   | μV/°C |   |   |

### Dynamic Electrical Characteristics T<sub>A</sub> = 25°C unless otherwise stated

| PARAMETER                                                      | SYMBOL          | TEST<br>CONDITIONS                                                          | MIN | TYP                    | MAX | UNITS |  |

|----------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------|-----|------------------------|-----|-------|--|

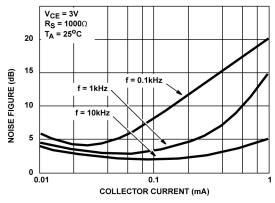

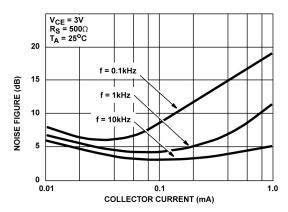

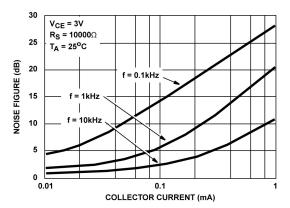

| Low Frequency Noise Figure (Figure 9)                          | NF              | $f$ = 1 kHz, $V_{CE}$ = 3V $I_{C}$ = 100μA, Source Resistance = 1k $\Omega$ | -   | 3.25                   | -   | dB    |  |

| Low Frequency, Small Signal Equivalent Circuit Characteristics |                 |                                                                             |     |                        |     |       |  |

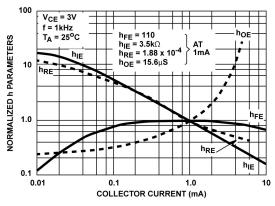

| Forward Current Transfer Ratio (Figure 11)                     | h <sub>FE</sub> | f = 1  kHz<br>$V_{CE} = 3V, I_C = 1\text{mA}$                               | -   | 110                    | -   | -     |  |

| Short Circuit Input Impedance<br>(Figure 11)                   | h <sub>IE</sub> | f = 1  kHz<br>$V_{CE} = 3V, I_C = 1\text{mA}$                               | -   | 3.5                    | -   | kΩ    |  |

| Open Circuit Output Impedance<br>(Figure 11)                   | h <sub>OE</sub> | f = 1  kHz<br>$V_{CE} = 3V, I_C = 1\text{mA}$                               | -   | 15.6                   | -   | μmho  |  |

| Open Circuit Reverse Voltage<br>Transfer Ratio (Figure 11)     | h <sub>RE</sub> | f = 1  kHz<br>$V_{CE} = 3V, I_C = 1\text{mA}$                               | -   | 1.8 x 10 <sup>-4</sup> | -   | -     |  |

Rev 1.1 20/10/17

#### Dynamic Electrical Characteristics continued T<sub>A</sub> = 25°C unless otherwise stated

| PARAMETER                                  | SYMBOL          | TEST<br>CONDITIONS                               | MIN | TYP         | MAX | UNITS |  |  |

|--------------------------------------------|-----------------|--------------------------------------------------|-----|-------------|-----|-------|--|--|

| Admittance Characteristics                 |                 |                                                  |     |             |     |       |  |  |

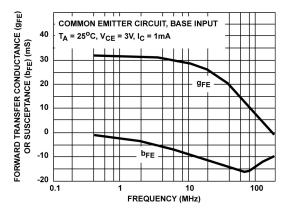

| Forward Transfer Admittance (Figure 12)    | Y <sub>FE</sub> | f = 1  kHz<br>$V_{CE} = 3V, I_{C} = 1 \text{mA}$ | -   | 31 - j1.5   | -   | -     |  |  |

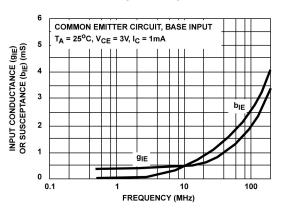

| Input Admittance (Figure 13)               | Y <sub>IE</sub> | f = 1  kHz<br>$V_{CE} = 3V, I_C = 1\text{mA}$    | -   | 0.3 + j0.04 | -   | -     |  |  |

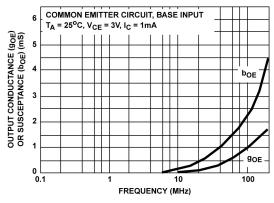

| Output Admittance (Figure 14)              | Y <sub>OE</sub> | f = 1  kHz<br>$V_{CE} = 3V, I_C = 1\text{mA}$    | -   | 0.001+j0.03 | -   | -     |  |  |

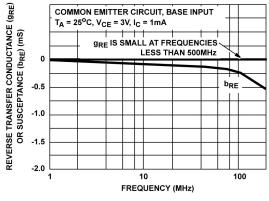

| Reverse Transfer Admittance<br>(Figure 15) | Y <sub>RE</sub> | f = 1  kHz<br>$V_{CE} = 3V, I_C = 1\text{mA}$    | -   | Fig 14      | -   | -     |  |  |

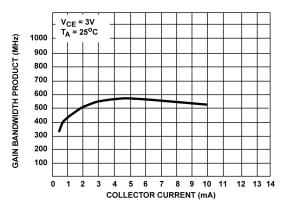

| Gain Bandwidth Product (Figure 16)         | f <sub>T</sub>  | $V_{CE} = 3V$ , $I_C = 1mA$                      | 300 | 550         | -   | MHz   |  |  |

| Emitter-to-Base Capacitance                | C <sub>EB</sub> | $V_{EB} = 3V, I_{E} = 0$                         | -   | 0.6         | -   | pF    |  |  |

| Collector-to-Base Capacitance              | C <sub>CB</sub> | $V_{CB} = 3V, I_{C} = 0$                         | -   | 0.58        | -   | pF    |  |  |

| Collector-to-Substrate Capacitance         | C <sub>CI</sub> | $V_{CS} = 3V, I_{C} = 0$                         | -   | 2.8         | -   | pF    |  |  |

Notes: 1. Each transistor collector is isolated from the substrate by an integral diode. The substrate (Pin 13) must be connected to the most negative point in the external circuit to maintain isolation between transistors & normal transistor action. 2. Actual forcing current is via the emitter for this test.

#### Typical Performance Characteristics

FIGURE 1. Base-To-Collector Current vs Temperature

FIGURE 3. Static Forward Current Transfer Ratio & Beta Ratio for  $Q_1$  and  $Q_2$  vs Emitter Current

FIGURE 2. Collector-To-Emitter Cutoff Current vs Temperature

**FIGURE 4.** Input Offset Current for matched transistor pair Q<sub>1</sub>Q<sub>2</sub> vs Collector Current

Rev 1.1 20/10/17

### Typical Performance Characteristics (Continued)

FIGURE 5. Static Base-to-Emitter Voltage characteristics and Input Offset Voltage for differential pair and paired isolated transistors vs Emitter Current

FIGURE 7. Input Offset Voltage characteristics for differential pair and paired isolated transistors vs Temperature

FIGURE 9. Noise Figure vs Collector Current

**FIGURE 6.** Base-to-Emitter Voltage characteristic vs Temperature for each transistor.

FIGURE 8. Noise Figure vs Collector Current

FIGURE 10. Noise Figure vs Collector Current

Rev 1.1 20/10/17

#### Typical Performance Characteristics (Continued)

FIGURE 11. Normalized Forward Current Transfer ratio, Short Circuit Input Impedance, Open Circuit Output Impedance, And Open Circuit Reverse Voltage Transfer Ratio vs Collector Current

FIGURE 13. Input Admittance vs Frequency

**FIGURE 15.** Typical Reverse Transfer Admittance vs Frequency

**FIGURE 12.** Forward Transfer Admittance vs Frequency

FIGURE 14. Output Admittance vs Frequency

FIGURE 16. Typical Gain Bandwidth Product vs Collector Current

Rev 1.1 20/10/17

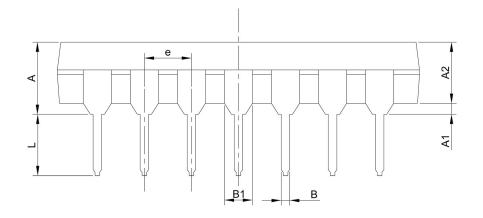

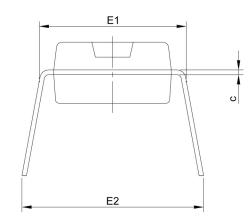

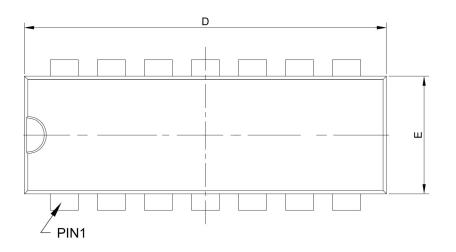

#### 14 Lead Plastic DIP - Package Dimensions and Footprint

| PKG. DIMENSIONS(MM) |          |       |  |  |  |  |

|---------------------|----------|-------|--|--|--|--|

| SYMBOL              | Min      | Max   |  |  |  |  |

| Α                   | 3.71     | 4.31  |  |  |  |  |

| A1                  | 0.51     |       |  |  |  |  |

| A2                  | 3.20     | 3.60  |  |  |  |  |

| В                   | 0.38     | 0.57  |  |  |  |  |

| B1                  | 1.52 BSC |       |  |  |  |  |

| С                   | 0.20     | 0.36  |  |  |  |  |

| D                   | 18.80    | 19.20 |  |  |  |  |

| E                   | 6.20     | 6.60  |  |  |  |  |

| E1                  | 7.32     | 7.92  |  |  |  |  |

| е                   | 2.54 BSC |       |  |  |  |  |

| L                   | 3.00     | 3.60  |  |  |  |  |

| E2                  | 8.40     | 9.00  |  |  |  |  |

|                     |          |       |  |  |  |  |

DISCLAIMER: The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Silicon Supplies Ltd hereby disclaims any and all warranties and liabilities of any kind.

LIFE SUPPORT POLICY: Silicon Supplies Ltd components may be used in life support devices or systems only with the express written approval of Silicon Supplies Ltd, if a failure of such components can reasonably be expected to cause the failure of that life support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.