CMOS High Voltage Logic - MM74C906M

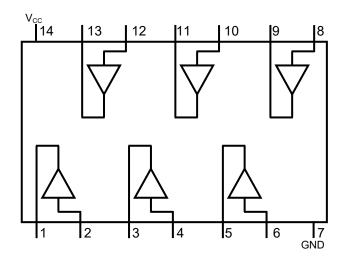

#### Hex Open Drain N-Channel Buffers in Plastic Small-Outline Package (SOIC)

Description

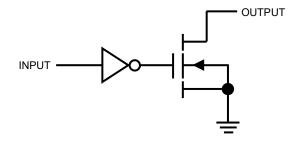

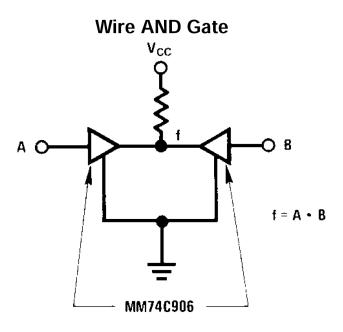

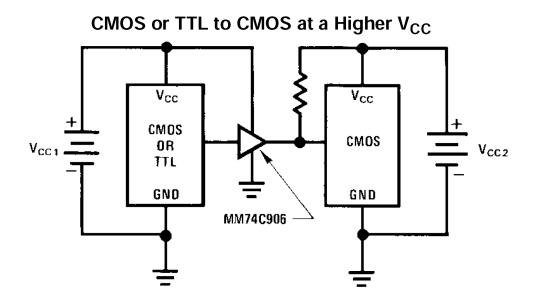

The MM74C906M buffer employs monolithic CMOS technology in achieving open drain outputs. The MM74C906M consists of six inverters driving six N-channel devices. The open-drain feature of these buffers makes level shifting or wire-AND and wire-OR functions by just the addition of pull-up or pull-down resistors. All inputs are protected from static discharge by diode clamps to  $V_{CC}$  and to ground.

## Features:

- Wide supply voltage range: 3V to 15V

- Guaranteed noise margin: 1V

- High noise immunity: 0.45 V<sub>CC</sub> (typ.)

- High current sourcing and sinking open-drain outputs

**Rev 1.0**

16/07/2021

# Ordering Information

The following part suffixes apply:

MM74C906M - 14 Lead Plastic SOIC Package

## Absolute Maximum Ratings<sup>1</sup>

# Schematic & Connection Diagram

| PARAMETER                                | SYMBOL               | VALUE                         | UNIT |  |

|------------------------------------------|----------------------|-------------------------------|------|--|

| Voltage at any input pin                 | V <sub>IN</sub>      | -0.3 to V <sub>CC</sub> + 0.3 | V    |  |

| Voltage at any output pin                | V <sub>OUT</sub>     | -0.3 to V <sub>CC</sub> + 0.3 | V    |  |

| Operating V <sub>CC</sub> range          | V <sub>CC</sub>      | 3 to 15                       | V    |  |

| Absolute maximum V <sub>CC</sub>         | V <sub>CC(MAX)</sub> | 18                            | V    |  |

| Maximum Power Dissipation                | PD                   | 700                           | mW   |  |

| Operating Temperature Range              | T <sub>A</sub>       | -40 to +85                    | °C   |  |

| Storage Temperature Range                | T <sub>STG</sub>     | -65 to +150                   | °C   |  |

| Lead Temperature (Soldering, 10 seconds) | TL                   | 260                           | °C   |  |

1. Operation above the absolute maximum rating may cause device failure. Operation at the absolute maximum ratings, for extended periods, may reduce device reliability.

CMOS High Voltage Logic - MM74C906M

### Rev 1.0 6/07/2021

| PARAMETER                 | SYMBOL             | MBOL TEST CONDITIONS                                                                                                                         |                          | TYP    | MAX | UNITS |

|---------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------|-----|-------|

| CMOS TO CMOS              |                    |                                                                                                                                              |                          |        |     |       |

| Logical "1" Input Voltage | V <sub>IN(1)</sub> | $V_{\rm CC}$ = 5V                                                                                                                            | 3.5                      | -      | -   | V     |

|                           |                    | V <sub>CC</sub> = 10V                                                                                                                        | 8.0                      | -      | -   | V     |

| Logical "0" Input Voltage | V <sub>IN(0)</sub> | $V_{CC} = 5V$                                                                                                                                | -                        | -      | 1.5 | V     |

|                           | ▼ IN(0)            | V <sub>CC</sub> = 10V                                                                                                                        | -                        | -      | 2.0 | V     |

| Logical "1" Input Current | I <sub>IN(1)</sub> | V <sub>CC</sub> = 15V, V <sub>IN</sub> = 15V                                                                                                 | -                        | 0.005  | 1   | μA    |

| Logical "0" Input Current | I <sub>IN(0)</sub> | V <sub>CC</sub> = 15V, V <sub>IN</sub> = 0V                                                                                                  | -1.0                     | -0.005 | -   | μA    |

| Supply Current            | I <sub>CC</sub>    | V <sub>CC</sub> = 15V,Output Open                                                                                                            | -                        | 0.05   | 15  | μA    |

| Output Leakage Current    |                    | $V_{CC} = 4.75V, \\ V_{IN} = V_{CC} - 1.5V, \\ V_{CC} = 4.75V, V_{OUT} = 18V$                                                                |                          | 0.005  | 5   | μA    |

| CMOS/LPTTL INTERFACE      |                    |                                                                                                                                              |                          |        |     |       |

| Logical "1" Input Voltage | V <sub>IN(1)</sub> | V <sub>CC</sub> = 4.75V                                                                                                                      | V <sub>CC</sub><br>-1.5V | -      | -   | V     |

| Logical "0" Input Voltage | V <sub>IN(0)</sub> | V <sub>CC</sub> = 4.75V                                                                                                                      | -                        | -      | 0.8 | V     |

| OUTPUT DRIVE CURRENT      |                    |                                                                                                                                              |                          |        |     |       |

|                           |                    | $\label{eq:V_CC} \begin{array}{ c c c } V_{CC} = 4.75V, \\ V_{IN} = 1V + 0.1 \ V_{CC}, \\ V_{CC} = 4.75V, \\ V_{OUT} = 0.5V \end{array}$     | 2.1                      | 8.0    | -   | mA    |

|                           |                    | $\label{eq:V_CC} \begin{array}{ c c c c c } V_{CC} = 4.75V, \\ V_{IN} = 1V + 0.1 \ V_{CC}, \\ V_{CC} = 4.75V, \\ V_{OUT} = 1.0V \end{array}$ | 4.2                      | 12.0   | -   | mA    |

|                           |                    | $\begin{tabular}{ c c c c c } \hline V_{CC} &= 10V, V_{IN} = 2V, \\ V_{CC} &= 10V, V_{OUT} = 0.5V \end{tabular}$                             | 4.2                      | 20     | -   | mA    |

|                           |                    | $V_{CC} = 10V, V_{IN} = 2V,$<br>$V_{CC} = 10V, V_{OUT} = 1V$                                                                                 | 8.4                      | 30     | -   | mA    |

# Dynamic Electrical Characteristics<sup>2</sup> $T_A = 25^{\circ}C$ unless otherwise stated

| PARAMETER                                  | SYMBOL           | TEST<br>CONDITIONS                                           | MIN | TYP | MAX | UNITS |

|--------------------------------------------|------------------|--------------------------------------------------------------|-----|-----|-----|-------|

| Propagation Delay Time<br>to Logical "0"   | t <sub>pd</sub>  | $V_{CC} = 5.0V,$<br>R = 10k $\Omega$ , C <sub>L</sub> = 50pF | -   | -   | 150 | ns    |

| Propagation Delay Time<br>to Logical "1"   | t <sub>pd</sub>  | $V_{CC} = 10V,$<br>R = 10k $\Omega$ , C <sub>L</sub> = 50pF  | -   | -   | 75  | ns    |

| Input Capacitance                          | C <sub>IN</sub>  | -                                                            | -   | 5.0 | -   | pF    |

| Output Capacitance                         | C <sub>OUT</sub> | -                                                            | -   | 20  | -   | pF    |

| Power Dissipation Capacitance <sup>2</sup> | C <sub>PD</sub>  | -                                                            | -   | 30  | -   | pF    |

**2.** Per Buffer, used to determine the no-load dynamic power consumption:  $P_D = C_{PD} V_{CC}^2 f + I_{CC} V_{CC}$ .

# **Typical Applications**

Rev 1.0 16/07/2021

Note: Can be extended to more than 2 inputs

CMOS High Voltage Logic - MM74C906M

#### 16/07/2021 SOIC 14 - Package Dimensions and Footprint 8.65 🛆 0.10 C A-B 2X A 3 6 DETAIL"A" 0.22±0.03 D 14 8 6.0 3.9 4 0.10 C D 2X 🛆 0.20 C 2X PIN NO.1 (0.35) x 45° $4^{\circ} \pm 4^{\circ}$ \$ 0.31-0.51 **B** 3 6 0.25M C A-B D TOP VIEW // 0.10 C Η 1.75 MAX 1.25 MIN 0.25 GAUGE PLANE 0.10-0.25 1.27 DETAIL "A' SIDE VIEW (1.27)(0.6) NOTES: 1. Dimensions are in millimeters. Dimensions in ( ) for Reference Only. 2. Dimensioning and tolerancing conform to AMSEY14.5m-1994. 3. Datums A and B to be determined at Datum H. (5.40) 4. Dimension does not include interlead flash or protrusions. Interlead flash or protrusions shall not exceed 0.25mm per side. 5. The pin #1 indentifier may be either a mold or mark feature. 6. Does not include dambar protrusion. Allowable dambar protrusion shall be 0.10mm total in excess of lead width at maximum condition. (1.50) 7. Reference to JEDEC MS-012-AB. TYPICAL RECOMMENDED LAND PATTERN

DISCLAIMER: The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Silicon Supplies Ltd hereby disclaims any and all warranties and liabilities of any kind.

LIFE SUPPORT POLICY: Silicon Supplies Ltd components may be used in life support devices or systems only with the express written approval of Silicon Supplies Ltd, if a failure of such components can reasonably be expected to cause the failure of that life support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

**Rev 1.0**