#### Hex Schmitt Trigger Inverter in bare die form

## Description

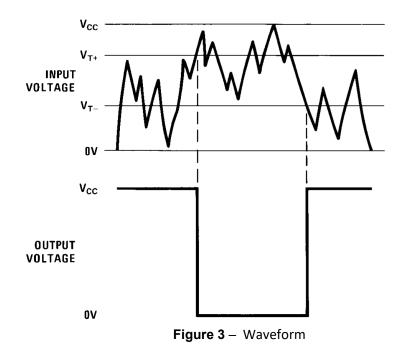

The MM74C14 Hex Schmitt Trigger is a monolithic complementary MOS (CMOS) integrated circuit constructed with N-channel and P-channel enhancement transistors. The positive and negative going threshold voltages, V<sub>T+</sub> and V<sub>T-</sub>, show low variation with respect to temperature (typ. 0.0005V/°C at V<sub>CC</sub> = 10V), and hysteresis, V<sub>T+</sub> - V<sub>T-</sub>  $\ge$  0.2 V<sub>CC</sub> is guaranteed. All inputs are protected from damage due to static discharge by diode clamps to V<sub>CC</sub> and GND.

#### Features:

Wide supply voltage range: 3V to 15V

**Rev 1.0**

17/02/2023

- High noise immunity: 0.70 V<sub>CC</sub> (typ.)

- Low power TTL compatibility:

- o 0.40 V<sub>CC</sub> (typ.)

- $\circ$  0.20 V<sub>CC</sub> (guaranteed)

- Hysteresis:

- o 0.40 V<sub>CC</sub> (typ.)

- $\circ$  ~ 0.20  $V_{CC}$  (guaranteed).

## **Ordering Information**

The following part suffixes apply:

No suffix - MIL-STD-883 /2010B Visual Inspection

For High Reliability versions of this product please see

MM54C14

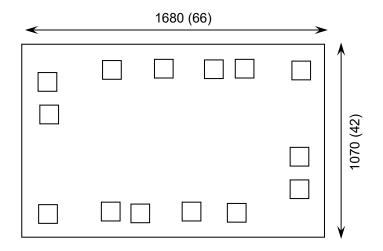

### Die Dimensions in µm (mils)

## Supply Formats:

- Default Die in Waffle Pack (100 per tray capacity)

- Sawn Wafer on Tape On request

- Unsawn Wafer On request

- Die Thickness <> 350µm(14 Mils) On request

- Assembled into Ceramic Package On request

## **Mechanical Specification**

| 1680 x 1070<br>66.14 x 42.13 | µm<br>mils                                                                               |  |

|------------------------------|------------------------------------------------------------------------------------------|--|

| 105 x 105<br>4.713 x 4.13    | µm<br>mils                                                                               |  |

| 350 (±20)<br>13.78 (±0.79)   |                                                                                          |  |

| Al 1%Si 1.1µm                |                                                                                          |  |

| N/A – Bare Si                |                                                                                          |  |

|                              | 66.14 x 42.13<br>105 x 105<br>4.713 x 4.13<br>350 (±20)<br>13.78 (±0.79)<br>Al 1%Si 1.1µ |  |

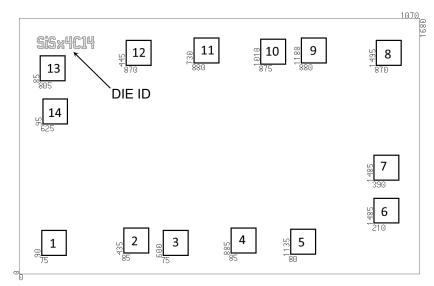

# Pad Layout and Functions

#### Rev 1.0 17/02/2023

| PAD | FUNCTION                             | COORDINATES (µm) |     |  |  |  |

|-----|--------------------------------------|------------------|-----|--|--|--|

| FAD | FUNCTION                             | X                | Y   |  |  |  |

| 1   | 1A                                   | 90               | 75  |  |  |  |

| 2   | 1Y                                   | 435              | 85  |  |  |  |

| 3   | 2A                                   | 600              | 75  |  |  |  |

| 4   | 2Y                                   | 885              | 85  |  |  |  |

| 5   | 3A                                   | 1135             | 80  |  |  |  |

| 6   | 3Y                                   | 1485             | 210 |  |  |  |

| 7   | GND                                  | 1485             | 390 |  |  |  |

| 8   | 4Y                                   | 1495             | 870 |  |  |  |

| 9   | 4A                                   | 1180             | 880 |  |  |  |

| 10  | 5Y                                   | 1010             | 875 |  |  |  |

| 11  | 5A                                   | 730              | 880 |  |  |  |

| 12  | 6Y                                   | 445              | 870 |  |  |  |

| 13  | 6A                                   | 85               | 805 |  |  |  |

| 14  | V <sub>cc</sub>                      | 95               | 625 |  |  |  |

|     | CONNECT CHIP BACK TO V <sub>CC</sub> |                  |     |  |  |  |

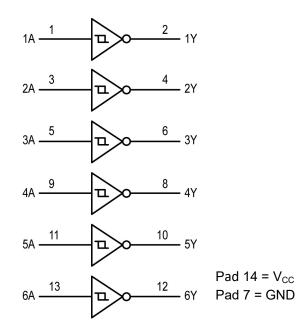

## Logic Diagram

# **Function Table**

| INPUT | OUTPUT |

|-------|--------|

| Α     | Y      |

| L     | Н      |

| Н     | L      |

#### Rev 1.0 17/02/2023

### Absolute Maximum Ratings<sup>1</sup>

| PARAMETER                              | SYMBOL               | VALUE                         | UNIT |

|----------------------------------------|----------------------|-------------------------------|------|

| Voltage at any input pin               | V <sub>IN</sub>      | -0.3 to V <sub>CC</sub> + 0.3 | V    |

| Voltage at any output pin              | V <sub>OUT</sub>     | -0.3 to V <sub>CC</sub> + 0.3 | V    |

| Operating V <sub>CC</sub> range        | V <sub>CC</sub>      | 3 to 15                       | V    |

| Absolute maximum V <sub>CC</sub>       | V <sub>CC(MAX)</sub> | 18                            | V    |

| Maximum Power Dissipation <sup>2</sup> | PD                   | 700                           | mW   |

| Operating Temperature Range            | T <sub>A</sub>       | -40 to +85                    | °C   |

| Storage Temperature Range              | T <sub>STG</sub>     | -65 to +150                   | °C   |

1. Operation above the absolute maximum rating may cause device failure. Operation at the absolute maximum ratings, for extended periods, may reduce device reliability. 2. Measured in plastic DIP package, results in die form are dependent on die attach and assembly method.

#### DC Electrical Characteristics T<sub>A</sub> = -40 to +85°C unless otherwise stated

| PARAMETER                        | SYMBOL                            | TEST CONDITIONS                               | MIN  | TYP    | MAX  | UNITS |

|----------------------------------|-----------------------------------|-----------------------------------------------|------|--------|------|-------|

| CMOS TO CMOS                     |                                   |                                               |      |        |      |       |

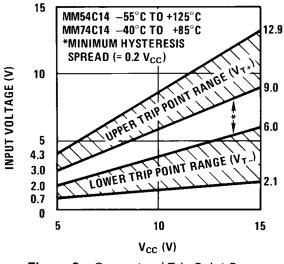

| Positive Going Threshold Voltage |                                   | $V_{\rm CC}$ = 5V                             | 3.0  | 3.6    | 4.3  | V     |

|                                  | V <sub>T+</sub>                   | V <sub>CC</sub> = 10V                         | 6.0  | 6.8    | 8.6  | V     |

|                                  |                                   | V <sub>CC</sub> = 15V                         | 9.0  | 10.0   | 12.9 | V     |

|                                  |                                   | $V_{\rm CC}$ = 5V                             | 0.7  | 1.4    | 2.0  | V     |

| Negative Going Threshold Voltage | V <sub>T-</sub>                   | V <sub>CC</sub> = 10V                         | 1.4  | 3.2    | 4.0  | V     |

|                                  |                                   | V <sub>CC</sub> = 15V                         | 2.1  | 5.0    | 6.0  | V     |

| Hysteresis                       |                                   | $V_{CC} = 5V$                                 | 1.0  | 2.2    | 3.6  | V     |

|                                  | V <sub>T+</sub> - V <sub>T-</sub> | V <sub>CC</sub> = 10V                         | 2.0  | 3.6    | 7.2  | V     |

|                                  |                                   | V <sub>CC</sub> = 15V                         | 3.0  | 5.0    | 10.8 | V     |

| Logical "1" Output Voltage       | V <sub>OUT(1)</sub>               | $V_{CC} = 5V, I_0 = -10\mu A$                 | 4.5  | -      | -    | V     |

| Logical 1 Output voltage         |                                   | $V_{CC} = 10V, I_{O} = -10\mu A$              | 9.0  | -      | -    | V     |

| Logical "0" Output Voltage       | V                                 | $V_{CC} = 5V, I_0 = 10\mu A$                  | -    | -      | 0.5  | V     |

| Logical o Output voltage         | V <sub>OUT(0)</sub>               | $V_{CC} = 10V, I_0 = 10\mu A$                 | -    | -      | 1.0  | V     |

| Logical "1" Input Current        | I <sub>IN(1)</sub>                | V <sub>CC</sub> = 15V, V <sub>IN</sub> = 15V  | -    | 0.005  | 1.0  | μA    |

| Logical "0" Input Current        | I <sub>IN(0)</sub>                | V <sub>CC</sub> = 15V, V <sub>IN</sub> = 0V   | -1.0 | -0.005 | -    | μA    |

| Supply Current                   | I <sub>CC</sub>                   | V <sub>CC</sub> =15V,V <sub>IN</sub> =0V/15V  | -    | 0.05   | 15   | μA    |

| Supply Current <sup>3</sup>      |                                   | $V_{CC} = 5V, V_{IN} = 2.5V$                  | -    | 20     | -    | μA    |

|                                  | I <sub>CC</sub>                   | $V_{CC} = 10V, V_{IN} = 5V$                   | -    | 200    | -    | μA    |

|                                  |                                   | V <sub>CC</sub> = 15V, V <sub>IN</sub> = 7.5V | -    | 600    | -    | μA    |

3. Only one of the six inputs is at  $\frac{1}{2}$  V<sub>CC</sub>; the others are either at V<sub>CC</sub> or GND.

#### Rev 1.0 16/07/2021

| DC Electrical Characteristi                | <b>CS</b> T <sub>A</sub> = -40 to | +85°C unless otherwise s                            | stated    |        | 16  | 5/07/202 <sup>,</sup> |

|--------------------------------------------|-----------------------------------|-----------------------------------------------------|-----------|--------|-----|-----------------------|

| PARAMETER                                  | SYMBOL                            | TEST CONDITIONS                                     | MIN       | TYP    | MAX | UNITS                 |

| CMOS/LPTTL INTERFACE                       |                                   |                                                     |           |        |     |                       |

| Logical "1" Input Voltage                  | V <sub>IN(1)</sub>                | $V_{\rm CC} = 5V$                                   | 4.3       | -      | -   | V                     |

| Logical "0" Input Voltage                  | V <sub>IN(0)</sub>                | $V_{\rm CC} = 5V$                                   | -         | -      | 0.7 | V                     |

| Logical "1" Output Voltage                 | V <sub>OUT(1)</sub>               | V <sub>CC</sub> = 4.75V,<br>I <sub>O</sub> = -360µA | 2.4       | -      | -   | V                     |

| Logical "0" Output Voltage                 | V <sub>OUT(0)</sub>               | V <sub>CC</sub> =4.75V,<br>I <sub>O</sub> = 360µA   | -         | -      | 0.4 | V                     |

| OUTPUT DRIVE CURRENT $T_A = 25^{\circ}C$   |                                   |                                                     |           |        |     |                       |

| Output Source Current                      | I <sub>SOURCE</sub>               | $V_{\rm CC}$ = 5V, $V_{\rm OUT}$ = 0V               | -1.75     | -3.3   | -   | mA                    |

| (P-Channel)                                | ISOURCE                           | V <sub>CC</sub> = 10V, V <sub>OUT</sub> = 0V        | -8.0      | -15    | -   | mA                    |

| Output Source Current                      | law.uz                            | $V_{CC} = 5V, V_{OUT} = V_{CC}$                     | 1.75      | 3.6    | -   | mA                    |

| (N-Channel)                                | I <sub>SINK</sub>                 | $V_{CC}$ = 10V, $V_{OUT}$ = $V_{CC}$                | 8.0       | 16     | -   | mA                    |

| DYNAMIC ELECTRICAL CHARACTERI              | $STICS^4 T_A = 25$                | °C, C <sub>L</sub> = 50pF unless oth                | nerwise s | stated |     |                       |

| Propagation Delay                          | t <sub>PD0,</sub>                 | $V_{\rm CC}$ = 5V                                   | -         | 220    | 400 | ns                    |

| from Input to Output                       | t <sub>PD1</sub>                  | V <sub>CC</sub> = 10V                               | -         | 80     | 200 | ns                    |

| Input Capacitance                          | C <sub>IN</sub>                   | Any Input                                           | -         | 5.0    | -   | pF                    |

| Power Dissipation Capacitance <sup>5</sup> | C <sub>PD</sub>                   | Per Gate                                            | -         | 20     | -   | pF                    |

4. Not production tested in die form, characterized by chip design.

**5.** Used to determine the no-load dynamic power consumption:  $P_D = C_{PD} V_{CC}^2 f + I_{CC} V_{CC}$ .

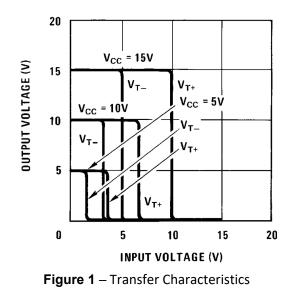

# **Typical Characteristics**

Figure 2 – Guaranteed Trip Point Range

# Typical Characteristics continued

Rev 1.0 16/07/2021

DISCLAIMER: The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Silicon Supplies Ltd hereby disclaims any and all warranties and liabilities of any kind.

LIFE SUPPORT POLICY: Silicon Supplies Ltd components may be used in life support devices or systems only with the express written approval of Silicon Supplies Ltd, if a failure of such components can reasonably be expected to cause the failure of that life support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.