#### Octal 3-State Inverting Buffer / Line Driver / Line Receiver in bare die form

## Description

The 54AC240 is produced on a 1.5µm 5V CMOS process combining high speed LSTTL performance with CMOS low power. The device can be used as two 4-bit buffers or one 8-bit buffer & features inverting inputs with two output enables, each controlling four of the 3-state outputs. The device is designed to improve performance & density in clock drivers, 3-state memory address drivers & bus orientated transmitters and receivers. Inputs accept standard CMOS outputs or LSTTL outputs using pull-up resistors. Inputs are also equipped with protection circuits against static discharge and transient excess voltage.

## Ordering Information

The following part suffixes apply:

- No suffix MIL-STD-883 /2010B Visual Inspection

- "H" MIL-STD-883 /2010B Visual Inspection + MIL-PRF-38534 Class H LAT

- "K" MIL-STD-883 /2010A Visual Inspection (Space) + MIL-PRF-38534 Class K LAT

LAT = Lot Acceptance Test.

For further information on LAT process flows see below.

www.siliconsupplies.com\quality\bare-die-lot-qualification

## Supply Formats:

- Default Die in Waffle Pack (100 per tray capacity)

- Sawn Wafer on Tape On request

- Unsawn Wafer On request

- Die Thickness <> 350µm(14 Mils) On request

- Assembled into Ceramic Package On request

### Features:

- Outputs Sink/Source 24mA

- Low Input Current: 1µA

- Outputs directly interface CMOS, NMOS and TTL

**Rev 1.1**

30/11/21

- Operating Voltage Range: 2V to 6V

- CMOS High Noise Immunity

- Function compatible with 54LS240

- Full Military Temperature Range.

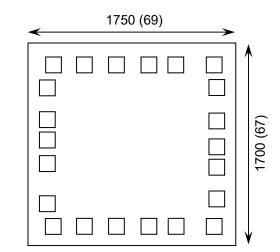

## Die Dimensions in µm (mils)

## **Mechanical Specification**

| Die Size (Unsawn)      | 1750 x 1700<br>69 x 67     | µm<br>mils |

|------------------------|----------------------------|------------|

| Minimum Bond Pad Size  | 130 x 130<br>5.12 x 5.12   | µm<br>mils |

| Die Thickness          | 350 (±20)<br>13.78 (±0.79) | µm<br>mils |

| Top Metal Composition  | Al 1%Si 1.1µm              |            |

| Back Metal Composition | N/A – Bare Si              |            |

### Rev 1.1 30/11/21

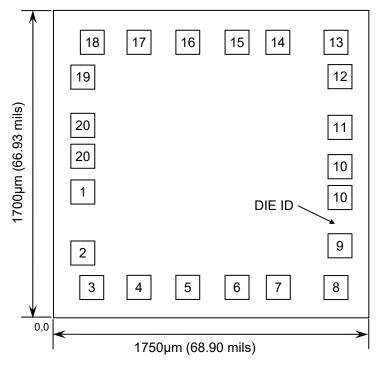

## Pad Layout and Functions

## Logic Diagram

| PAD | FUNCTION                               | COORDINATES (mm) |       |  |

|-----|----------------------------------------|------------------|-------|--|

|     | TONOTION                               | X                | Y     |  |

| 1   | 10E                                    | 0.100            | 0.630 |  |

| 2   | 1A1                                    | 0.100            | 0.290 |  |

| 3   | <u>2Y4</u>                             | 0.150            | 0.100 |  |

| 4   | 1A2                                    | 0.410            | 0.100 |  |

| 5   | <u>2Y3</u>                             | 0.680            | 0.100 |  |

| 6   | 1A3                                    | 0.950            | 0.100 |  |

| 7   | <u>2Y2</u>                             | 1.180            | 0.100 |  |

| 8   | 1A4                                    | 1.500            | 0.100 |  |

| 9   | <u>2Y1</u>                             | 1.520            | 0.330 |  |

| 10  | GND                                    | 1.520            | 0.600 |  |

| 10  | GND                                    | 1.520            | 0.770 |  |

| 11  | 2A1                                    | 1.520            | 0.990 |  |

| 12  | <u>1Y4</u>                             | 1.520            | 1.270 |  |

| 13  | 2A2                                    | 1.500            | 1.460 |  |

| 14  | <u>1Y3</u>                             | 1.180            | 1.460 |  |

| 15  | 2A3                                    | 0.950            | 1.460 |  |

| 16  | <u>1Y2</u>                             | 0.680            | 1.460 |  |

| 17  | 2A4                                    | 0.410            | 1.460 |  |

| 18  | <u>1Y1</u>                             | 0.150            | 1.460 |  |

| 19  | 20E                                    | 0.100            | 1.270 |  |

| 20  | V <sub>cc</sub>                        | 0.100            | 1.000 |  |

| 20  | V <sub>cc</sub>                        | 0.100            | 0.830 |  |

| CO  | CONNECT CHIP BACK TO $V_{CC}$ OR FLOAT |                  |       |  |

## Truth Table

| INP                                                                                                 | OUTPUTS     |             |  |  |  |

|-----------------------------------------------------------------------------------------------------|-------------|-------------|--|--|--|

| 10E<br>20E                                                                                          | 1A, 2A      | 1Y, 2Y      |  |  |  |

| L<br>L<br>H                                                                                         | L<br>H<br>X | H<br>L<br>Z |  |  |  |

| H = High level (steady state)<br>L = Low level (steady state)<br>X = Don't care, Z = High impedance |             |             |  |  |  |

### **Pad Descriptions**

#### ADDRESS INPUTS

1A1, 1A2, 1A3, 1A4, 2A1, 2A2, 2A3, 2A4 (Pads 2, 4, 6, 8, 11, 13, 15, 17) Data input pins. Data on these pins appear in inverted form on the corresponding Y outputs, when the outputs are enabled.

#### CONTROL INPUTS

10E, 20E (Pads 1, 19)

Output enables (active-low). When a low level is applied to these pins, the outputs are enabled and the devices function as inverters. When a high level is applied, the outputs assume the high impedance state.

#### OUTPUTS

1Y1, 1Y2, 1Y3, 1Y4, 2Y1, 2Y2, 2Y3, 2Y4

(Pads 18, 16, 14, 12, 9, 7, 5, 3)

Device outputs. Depending upon the state of the output enable pins, these outputs are either inverting outputs or high-impedance outputs.

### Absolute Maximum Ratings<sup>1</sup>

| PARAMETER                                   | SYMBOL           | VALUE                        | UNIT |

|---------------------------------------------|------------------|------------------------------|------|

| DC Supply Voltage (Referenced to GND)       | V <sub>CC</sub>  | -0.5 to +7.0                 | V    |

| DC Input Voltage (Referenced to GND)        | V <sub>IN</sub>  | -0.5 to V <sub>CC</sub> +0.5 | V    |

| DC Output Voltage (Referenced to GND)       | V <sub>OUT</sub> | -0.5 to V <sub>CC</sub> +0.5 | V    |

| DC Input Current, per pin                   | I <sub>IN</sub>  | ±20                          | mA   |

| DC Output Current, per pin                  | I <sub>OUT</sub> | ±50                          | mA   |

| DC V <sub>CC</sub> or GND Current, per pin  | I <sub>CC</sub>  | ±50                          | mA   |

| Power Dissipation in Still Air <sup>2</sup> | PD               | 750                          | mW   |

| Storage Temperature Range                   | T <sub>STG</sub> | -65 to 150                   | °C   |

1. Operation above the absolute maximum rating may cause device failure. Operation at the absolute maximum ratings, for extended periods, may reduce device reliability. 2. Measured in plastic DIP package, results in die form are dependent on die attach and assembly method.

## Recommended Operating Conditions<sup>3</sup> (Voltages referenced to GND)

| PARAMETER                                                     |                        | SYMBOL                            | MIN | MAX             | UNITS |

|---------------------------------------------------------------|------------------------|-----------------------------------|-----|-----------------|-------|

| DC Supply Voltage                                             |                        | V <sub>CC</sub>                   | 2   | 6               | V     |

| DC Input or Output Voltage                                    |                        | V <sub>IN</sub> ,V <sub>OUT</sub> | 0   | V <sub>CC</sub> | V     |

| Operating Temperature Range                                   |                        | TJ                                | -55 | +125            | °C    |

| Output Current – High                                         |                        | I <sub>OH</sub>                   | -   | -24             | mA    |

| Output Current – Low                                          |                        | I <sub>OL</sub>                   | -   | 24              | mA    |

| Input Rise and Fall Time<br>(V <sub>IN</sub> from 30% to 70%) | V <sub>CC</sub> = 3.0V |                                   | 0   | 150             |       |

|                                                               | $V_{CC} = 4.5V$        | t <sub>r</sub> , t <sub>f</sub>   | 0   | 40              | ns/V  |

|                                                               | $V_{\rm CC} = 5.5 V$   |                                   | 0   | 24              |       |

3. This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation,  $V_{IN}$  and  $V_{OUT}$  should be constrained to the range GND  $\leq (V_{IN} \text{ or } V_{OUT}) \leq V_{CC}$ . Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or  $V_{CC}$ ). Unused outputs must be left open.

Rev 1.1 30/11/21

#### Rev 1.1 30/11/21

| PARAMETER                           | SYMBOL                                                          | V <sub>cc</sub> | CONDITIONS                                                               |      | LIMI | TS                      |    |

|-------------------------------------|-----------------------------------------------------------------|-----------------|--------------------------------------------------------------------------|------|------|-------------------------|----|

| FARAIVIETER                         | STWBUL                                                          | VCC             | CONDITIONS                                                               | 25°C | 85°C | FULL RANGE <sup>4</sup> |    |

| Minimum High-Level<br>Input Voltage | V <sub>IH</sub>                                                 | 3.0V            | V <sub>OUT</sub> = 0.1V or                                               | 2.1  | 2.1  | 2.1                     | V  |

|                                     |                                                                 | 4.5V            | V <sub>CC</sub> -0.1V                                                    | 3.15 | 3.15 | 3.15                    |    |

|                                     |                                                                 | 5.5V            | I <sub>OUT</sub>   ≤ 20μA                                                | 3.85 | 3.85 | 3.85                    |    |

|                                     |                                                                 | 3.0V            | V <sub>OUT</sub> = 0.1V or                                               | 0.9  | 0.9  | 0.9                     | V  |

| Maximum Low-Level<br>Input Voltage  | VIL                                                             | 4.5V            | V <sub>cc</sub> -0.1V                                                    | 1.35 | 1.35 | 1.35                    |    |

| par renage                          |                                                                 | 5.5V            | I <sub>OUT</sub>   ≤ 20μA                                                | 1.65 | 1.65 | 1.65                    |    |

|                                     |                                                                 | 3.0V            |                                                                          | 2.9  | 2.9  | 2.9                     |    |

|                                     |                                                                 | 4.5V            | Ι <sub>ΟUT</sub> = -50μΑ                                                 | 4.4  | 4.4  | 4.4                     |    |

|                                     |                                                                 | 5.5V            |                                                                          | 5.4  | 5.4  | 5.4                     |    |

| Minimum High-Level                  |                                                                 | 3.0V            | $V_{IN} = V_{IL} \text{ or } V_{IH}$<br>$I_{OH} = -12 \text{ mA}$        | 2.56 | 2.46 | 2.40                    | V  |

| Output Voltage                      |                                                                 | 4.5V            | $V_{IN} = V_{IL} \text{ or } V_{IH}$<br>$I_{OH} = -24 \text{ mA}^5$      | 3.86 | 3.76 | 3.70                    |    |

|                                     |                                                                 | 5.5V            | $V_{IN} = V_{IL} \text{ or } V_{IH}$<br>$I_{OH} = -24 \text{ mA}^5$      | 4.86 | 4.76 | 4.70                    |    |

|                                     |                                                                 | 5.5V            | $V_{IN} = V_{IL} \text{ or } V_{IH}$<br>$I_{OH} = -50 \text{mA}^6$       | -    | -    | 3.85                    |    |

|                                     | V <sub>OL</sub><br>3.0V<br>4.5V<br>3.0V<br>4.5V<br>5.5V<br>5.5V | 3.0V            |                                                                          | 0.1  | 0.1  | 0.1                     |    |

|                                     |                                                                 | 4.5V            | Ι <sub>ουτ</sub> = 50μΑ                                                  | 0.1  | 0.1  | 0.1                     |    |

|                                     |                                                                 | 5.5V            |                                                                          | 0.1  | 0.1  | 0.1                     |    |

| Maximum Low-Level                   |                                                                 | 3.0V            | $V_{IN} = V_{IH} \text{ or } V_{IL}$<br>$ I_{OUT}  \le 12 \text{mA}$     | 0.36 | 0.44 | 0.5                     |    |

| Output Voltage                      |                                                                 | 4.5V            | $V_{IN} = V_{IH} \text{ or } V_{IL}$<br>$ I_{OUT}  \le 24 \text{mA}^5$   | 0.36 | 0.44 | 0.5                     | V  |

|                                     |                                                                 | 5.5V            | $V_{IN} = V_{IH} \text{ or } V_{IL}$<br>$ I_{OUT}  \le 24 \text{mA}^5$   | 0.36 | 0.44 | 0.5                     |    |

|                                     |                                                                 | 5.5V            | $V_{IN} = V_{IH} \text{ or } V_{IL}$<br>$ I_{OUT}  50mA^{6}$             | -    | -    | 1.65                    |    |

| Maximum Input<br>Leakage Current    | I <sub>IN</sub>                                                 | 5.5V            | $V_{IN} = V_{CC}$ or GND                                                 | ±0.1 | ±1.0 | ±1.0                    | μA |

| Maximum 3-State<br>Leakage Current  | I <sub>oz</sub>                                                 | 5.5V            | $V_{OUT}=V_{CC} \text{ or } GND$<br>$V_{IN} = V_{IL} \text{ or } V_{IH}$ | ±0.5 | ±2.5 | ±5                      | μA |

| Minimum Dynamic                     | I <sub>OLD</sub>                                                | 5.5V            | V <sub>OLD</sub> = 1.65V Max                                             | -    | 75   | 50                      | A  |

| Output Current <sup>7</sup>         | I <sub>OHD</sub>                                                | 5.5V            | V <sub>OHD</sub> = 3.85V Min                                             | -    | -75  | -50                     | mA |

| Maximum Quiescent<br>Supply Current | I <sub>CC</sub>                                                 | 5.5V            | $V_{IN} = V_{CC}$ or GND<br>$I_{OUT} = 0\mu A$                           | 8    | 80   | 160                     | μA |

**4.**  $-55^{\circ}C \le T_{J} \le +125^{\circ}C$  **5.** All outputs loaded; thresholds on input associated with output under test. **6.** Test time 1sec max, measurement made by forcing indicated current and measuring voltage to minimize power dissipation. Test verifies a minimum 75 $\Omega$  transmission-line drive capability at 125°C **7.** Maximum test duration 2ms, one output loaded at a time

#### Rev 1.1 30/11/21

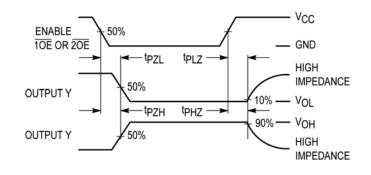

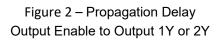

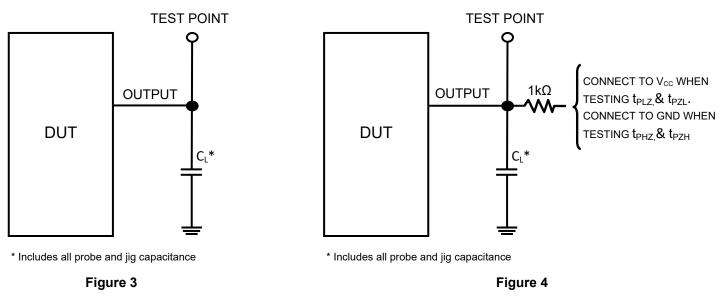

#### AC Electrical Characteristics<sup>8</sup> (V<sub>cc</sub> 3.3V ±0.3V, V<sub>cc</sub> 5V ±0.3V) LIMITS PARAMETER SYMBOL Vcc CONDITIONS UNITS 25°C 85°C **FULL RANGE<sup>4</sup>** $C_{1} = 50 pF_{1}$ 8.0 11.0 3.3V 9.0 Input t<sub>PLH,</sub> ns Maximum 7.0 8.5 6.5 5.0V $t_r = t_f = 3ns$ Propagation Delay Input A to Output Y $C_{L} = 50 pF$ , 8.0 8.5 10.5 3.3V (Figure 1,3) t<sub>PHI</sub> Input ns 5.0V $t_r = t_f = 3ns$ 6.0 6.5 8.0 $C_{L} = 50 pF$ , 10.5 11.0 11.5 3.3V Input ns t<sub>PZH.</sub> **Output Enable Time** 7.0 9.0 5.0V $t_r = t_f = 3ns$ 8.0 OE to 1Y or 2Y $C_{L} = 50 pF$ , (Figure 2,4) 10.0 11.0 13.0 3.3V Input ns t<sub>PZL</sub> 5.0V $t_r = t_f = 3ns$ 8.0 8.5 10.5 $C_{L} = 50 pF$ , 10.5 3.3V 10 12.5 Input t<sub>PHZ</sub> ns **Output Enable Time** $t_r = t_f = 3ns$ 9.0 9.5 10.5 5.0V OE to 1Y or 2Y $C_{L} = 50 pF$ , (Figure 2,4) 3.3V 10.5 11.5 13.5 Input t<sub>PLZ</sub> ns 5.0V $t_r = t_f = 3ns$ 9.0 9.5 11.0 Maximum Input 4.5 4.5 4.5 pF CIN --Capacitance TYPICAL Power Dissipation $T_{1} = 25^{\circ}C_{1}$ $C_{PD}$ \_ Capacitance<sup>9</sup> $V_{CC} = 5.0V$ 45 pF

8. Not production tested in die form, characterized by chip design

**9.** Used to determine the no-load dynamic power consumption:  $P_D = C_{PD} V_{CC}^2 f + I_{CC} V_{CC}$ .

#### Rev 1.1 30/11/21

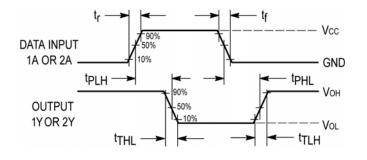

## Switching Waveforms

Figure 1 – Propagation Delay Input 1A or 2A to Output 1Y or 2Y

## **Test Circuits**

DISCLAIMER: The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Silicon Supplies Ltd hereby disclaims any and all warranties and liabilities of any kind.

LIFE SUPPORT POLICY: Silicon Supplies Ltd components may be used in life support devices or systems only with the express written approval of Silicon Supplies Ltd, if a failure of such components can reasonably be expected to cause the failure of that life support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.