# **CPM2-1200-0160A** Silicon Carbide Power MOSFET C2M<sup>™</sup> MOSFET Technology

N-Channel Enhancement Mode

## Features

- C2M SiC MOSFET technlogy

- High Blocking Voltage with Low On-Resistance

- High Speed Switching with Low Capacitances

- Easy to Parallel and Simple to Drive

- Avalanche Ruggedness

- Resistant to Latch-Up

- Halogen Free, RoHS Compliant

#### **Benefits**

- Higher System Efficiency

- Reduced Cooling Requirements

- Increased Power Density

- Increased System Switching Frequency

# Applications

- Solar Inverters

- Switch Mode Power Supplies

- High Voltage DC/DC Converters

- LED Lighting Power Supplies

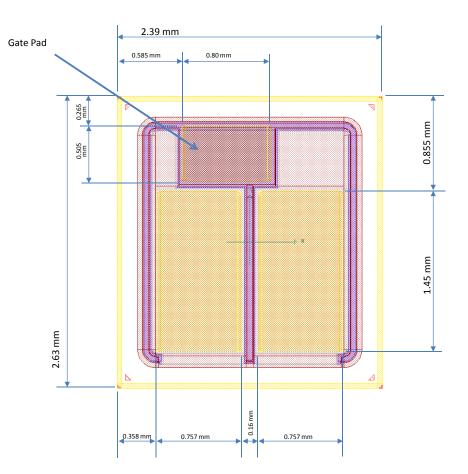

| Part Number     | Die Size (mm) |  |  |

|-----------------|---------------|--|--|

| CPM2-1200-0160A | 2.39 × 2.63   |  |  |

G

(1)

| Maximum | Ratings | $(T_{c} = 25 °C)$ | unless | otherwise s | specified) |

|---------|---------|-------------------|--------|-------------|------------|

|---------|---------|-------------------|--------|-------------|------------|

| Symbol                  | Parameter                                  | Value          | Unit | Test Conditions                                              | Note |

|-------------------------|--------------------------------------------|----------------|------|--------------------------------------------------------------|------|

| $V_{\text{DSmax}}$      | Drain - Source Voltage                     | 1200           | V    | $V_{\text{GS}}$ = 0 V, $I_{\text{D}}$ = 100 $\mu\text{A}$    |      |

| $V_{\text{GSmax}}$      | Gate - Source Voltage                      | -10/+25        | V    | Absolute maximum values                                      |      |

| $V_{GSop}$              | Gate - Source Voltage                      | -5/+20         | V    | Recommended operational values                               |      |

| I <sub>D</sub>          | In Continuous Drain Current                | 18             | A    | $V_{GS} = 20 \text{ V}, \text{ T}_{C} = 25^{\circ}\text{C}$  |      |

| LD                      |                                            | 13.8           |      | $V_{GS} = 20 \text{ V}, \text{ T}_{C} = 100^{\circ}\text{C}$ |      |

| $\mathbf{I}_{D(pulse)}$ | Pulsed Drain Current                       | 40             | А    | Pulse width $t_p$ limited by $T_{jmax}$                      |      |

| $T_{j}$ , $T_{stg}$     | Operating Junction and Storage Temperature | -55 to<br>+175 | °C   |                                                              |      |

| TL                      | Solder Temperature                         | 260            | °C   | 1.6mm (0.063") from case for 10s                             |      |

| T <sub>Proc</sub>       | Maximum Processing Temperature             | 325            | °C   | 10 min. maximum                                              |      |

V<sub>DS</sub>

1200 V

I<sub>D</sub>@25°C

18 A

R<sub>DS(on)</sub>

160 mΩ

D (2)

(3)

# Chip Outline

CPM2-1200-0160A Rev. 1, 09-2020

| Symbol                      | Parameter                        | Min. | Тур. | Max. | Unit                   | Test Conditions                                                         | Note            |

|-----------------------------|----------------------------------|------|------|------|------------------------|-------------------------------------------------------------------------|-----------------|

| $V_{(\text{BR})\text{DSS}}$ | Drain-Source Breakdown Voltage   | 1200 |      |      | V                      | $V_{GS} = 0 V, I_{D} = 100 \mu A$                                       |                 |

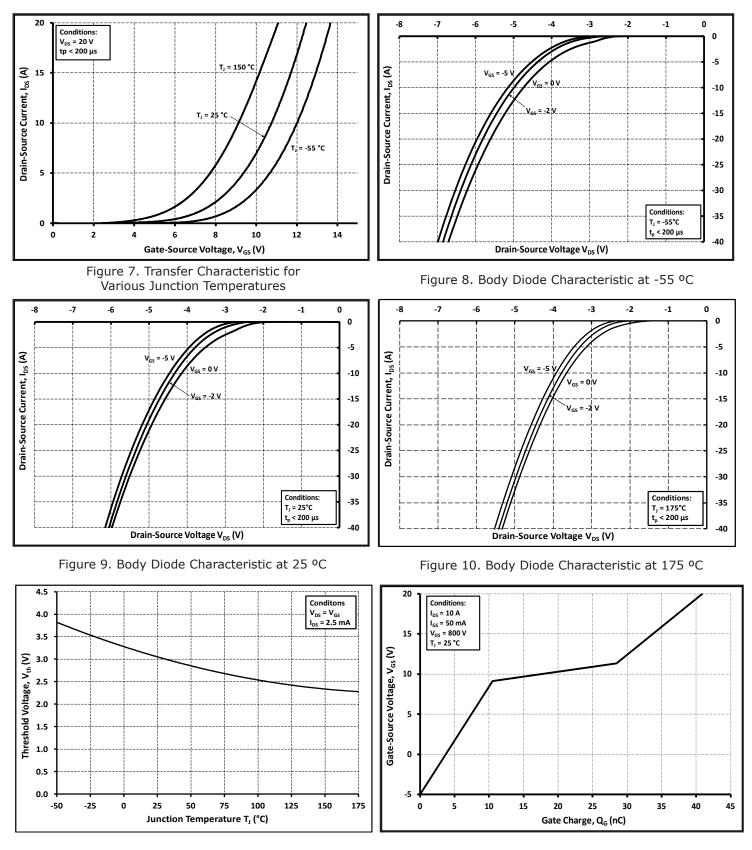

| N/                          | Cate Threehold Voltage           | 2.0  | 3.0  | 4.0  | V                      | $V_{\text{DS}}$ = $V_{\text{GS}}$ , $I_{\text{DS}}$ = 2.5 mA            |                 |

| $V_{GS(th)}$                | Gate Threshold Voltage           |      | 2.25 |      | V                      | $V_{DS} = V_{GS}, I_{DS} = 2.5 \text{ mA}, T_{J} = 175^{\circ}\text{C}$ | Fig. 11         |

| $\mathbf{I}_{DSS}$          | Zero Gate Voltage Drain Current  |      | 1    | 100  | μA                     | $V_{DS} = 1200 V, V_{GS} = 0 V$                                         |                 |

| $\mathbf{I}_{GSS}$          | Gate-Source Leakage Current      |      |      | 250  | nA                     | $V_{GS}$ = 20 V, $V_{DS}$ = 0 V                                         |                 |

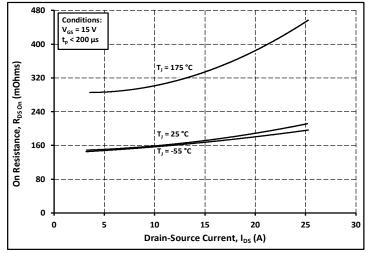

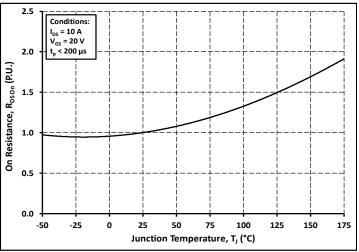

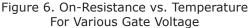

| D                           | Drain-Source On-State Resistance |      | 160  | 196  | mΩ                     | $V_{\text{GS}}$ = 20 V, $I_{\text{D}}$ = 10 A                           | Fig. 4,<br>5, 6 |

| $R_{DS(on)}$                |                                  |      | 306  |      | 11132                  | $V_{\text{GS}}$ = 20 V, $I_{\text{D}}$ = 10A, $T_{\text{J}}$ = 175°C    |                 |

| a Transconductanco          | Transconductance                 |      | 3.8  |      | S                      | $V_{\text{DS}}\text{=}$ 20 V, $I_{\text{DS}}\text{=}$ 10 A              | Fig. 7          |

| <b>g</b> <sub>fs</sub>      |                                  |      | 5.34 |      |                        | $V_{DS}$ = 20 V, $I_{DS}$ = 10 A, $T_{J}$ = 150°C                       |                 |

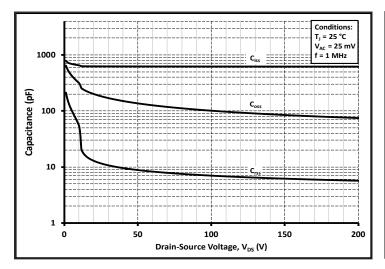

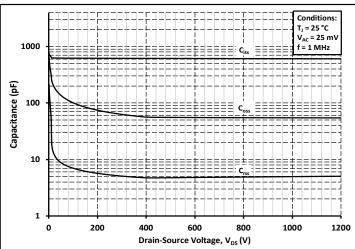

| $C_{\text{iss}}$            | Input Capacitance                |      | 606  |      |                        | $V_{GS} = 0 V$                                                          | Fig. 17,<br>18  |

| $C_{\text{oss}}$            | Output Capacitance               |      | 55   |      | pF                     | $V_{\rm DS} = 1000  \rm V$                                              |                 |

| $C_{rss}$                   | Reverse Transfer Capacitance     |      | 5    |      |                        | f = 1 MHz                                                               |                 |

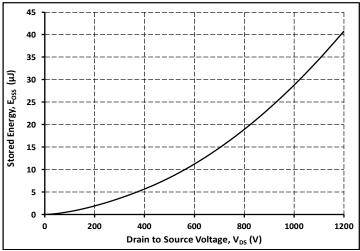

| E <sub>oss</sub>            | Coss Stored Energy               |      | 28   |      | μJ                     | V <sub>AC</sub> = 25 mV                                                 | Fig. 16         |

| $R_{G(int)}$                | Internal Gate Resistance         |      | 6.8  |      | Ω                      | $f = 1 MHz$ , $V_{AC} = 25 mV$                                          |                 |

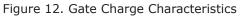

| $Q_{\text{gs}}$             | Gate to Source Charge            |      | 11   |      |                        | V <sub>DS</sub> = 800 V, V <sub>GS</sub> = -5/20 V                      | Fig. 12         |

| $Q_{\text{gd}}$             | Gate to Drain Charge             |      | 17   |      | nC                     | $I_D = 10 A$                                                            |                 |

| Qg                          | Total Gate Charge                |      | 40   |      | Per IEC60747-8-4 pg 21 |                                                                         |                 |

# **Electrical Characteristics** ( $T_c = 25^{\circ}C$ unless otherwise specified)

# **Reverse Diode Characteristics**

| Symbol           | Parameter                        | Тур. | Max. | Unit | Test Conditions                                                     | Note      |

|------------------|----------------------------------|------|------|------|---------------------------------------------------------------------|-----------|

| N                | Diada Famuard Valtage            | 3.9  |      | V    | $V_{GS} = -5 V, I_F = 5 A$                                          | Fig. 8,9, |

| V <sub>SD</sub>  | Diode Forward Voltage            | 3.4  |      | V    | $V_{GS} = -5V, I_F = 5 A, T_J = 175 \text{ °C}$                     | 10        |

| Is               | Continuous Diode Forward Current |      | 30   | А    | $T_c = 25^{\circ}C$                                                 |           |

| t <sub>rr</sub>  | Reverse Recovery Time            | 20   |      | ns   |                                                                     |           |

| Qrr              | Reverse Recovery Charge          | 192  |      | nC   | $V_{GS} = -5 V, I_{SD} = 10 A, V_{R} = 800 V$<br>dif/dt = 2400 A/µs |           |

| I <sub>rrm</sub> | Peak Reverse Recovery Current    | 16   |      | А    |                                                                     |           |

### **Typical Performance**

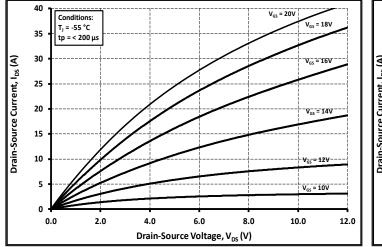

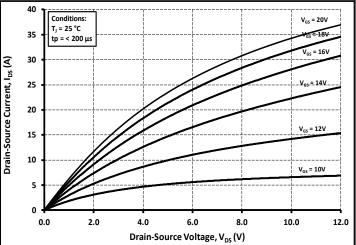

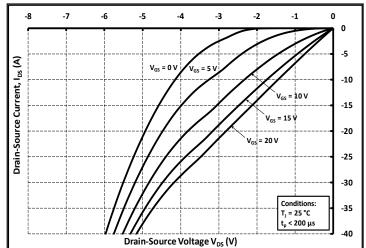

Figure 1. Output Characteristics  $T_J = -55 \text{ °C}$

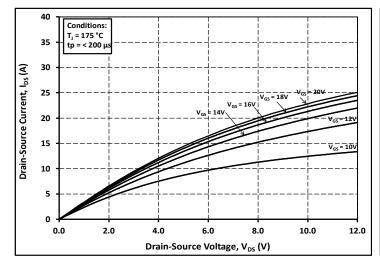

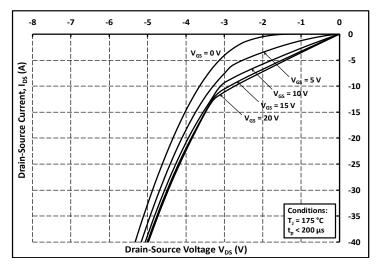

Figure 3. Output Characteristics T<sub>1</sub> = 175 °C

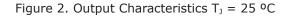

Figure 4. Normalized On-Resistance vs. Temperature

Figure 11. Threshold Voltage vs. Temperature

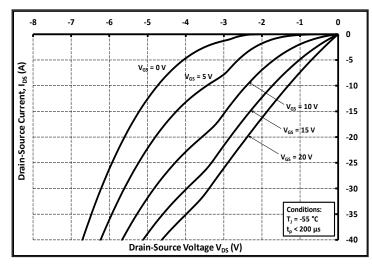

Figure 13. 3rd Quadrant Characteristic at -55 °C

Figure 15. 3rd Quadrant Characteristic at 175 °C

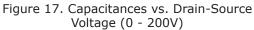

Figure 14. 3rd Quadrant Characteristic at 25 °C

Figure 16. Output Capacitor Stored Energy

Figure 18. Capacitances vs. Drain-Source Voltage (0 - 1000V)

## **Mechanical Parameters**

| Parameter                                      | Typical Value | Unit |

|------------------------------------------------|---------------|------|

| Die Dimensions (L x W)                         | 2.39 × 2.63   | mm   |

| Exposed Source Pad Metal Dimensions (LxW) Each | 0.757 × 1.45  | mm   |

| Gate Pad Dimensions (L x W)                    | 0.80 × 0.505  | mm   |

| Die Thickness                                  | 180 ± 20      | μm   |

| Top Side Source metallization (AI)             | 4             | μm   |

| Top Side Gate metallization (AI)               | 4             | μm   |

| Bottom Drain metallization (Ni/Au)             | 0.8 / 0.6     | μm   |

# **Chip Dimensions**

### **Revision History**

| Revision Number | Date of Change | Brief Summary    |

|-----------------|----------------|------------------|

| 1               | 09/11/2020     | Initial release. |

This product has not been designed or tested for use in, and is not intended for use in, applications implanted into the human body nor in applications in which failure of the product could lead to death, personal injury or property damage, including but not limited to equipment used in the operation of nuclear facilities, life-support machines, cardiac defibrillators or similar emergency medical equipment, aircraft navigation or communication or control systems, air traffic control systems, or weapons systems.

Cree, Inc. 4600 Silicon Drive Durham, NC 27703 USA Tel: +1.919.313.5300 Fax: +1.919.313.5451 www.cree.com/power

Copyright © 2020 Cree, Inc. All rights reserved. The information in this document is subject to change without notice. Cree and the Cree logo are registered trademarks and Z-REC and Z-FET are trademarks of Cree, Inc.

7

#### Notes

#### • RoHS Compliance

The levels of RoHS restricted materials in this product are below the maximum concentration values (also referred to as the threshold limits) permitted for such substances, or are used in an exempted application, in accordance with EU Directive 2011/65/EC (RoHS2), as implemented January 2, 2013. RoHS Declarations for this product can be obtained from your Cree representative or from the Product Documentation sections of www.cree.com.

#### • **REACh Compliance**

REACh substances of high concern (SVHCs) information is available for this product. Since the European Chemical Agency (ECHA) has published notice of their intent to frequently revise the SVHC listing for the foreseeable future, please contact a Cree representative to insure you get the most up-to-date REACh SVHC Declaration. REACh banned substance information (REACh Article 67) is also available upon request.

This product has not been designed or tested for use in, and is not intended for use in, applications implanted into

the human body nor in applications in which failure of the product could lead to death, personal injury or property

damage, including but not limited to equipment used in the operation of nuclear facilities, life-support machines,

cardiac defibrillators or similar emergency medical equipment, aircraft navigation or communication or control

systems, air traffic control systems.

#### **Related Links**

- C2M PSPICE Models: www.cree.com/power

- SiC MOSFET Isolated Gate Driver reference design: www.cree.com/power

- Application Considerations for Silicon-Carbide MOSFETs: www.cree.com/power

Copyright © 2020 Cree, Inc. All rights reserved. The information in this document is subject to change without notice. Cree, the Cree logo, and Zero Recovery are registered trademarks of Cree, Inc. Cree, Inc. 4600 Silicon Drive Durham, NC 27703 USA Tel: +1.919.313.5300 Fax: +1.919.313.5451 www.cree.com/power