#### 4-bit Binary Counter Logic IC in bare die form

Rev 1.1 28/08/21

#### Description

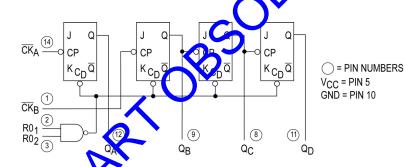

The 74ALS93 4-bit binary counter is fabricated using a 2µm 40V bipolar process. The device comprises two 4-bit ripple type counters consisting of four master-slave flip-flops internally connected to provide a divide-by-two section and a divide-by-eight section. Each section has independent clock (CK) & asynchronous master reset (R0) inputs. Counter state change is triggered by a high-to-low transition on the clock. Each section can be used separately or tied together (Q to CK) to form BCD or modulo-16 counters.

#### Features:

- Low Power Consumption

- Input Clamp Diodes Limit High Speed Termination Effects

- Direct drop-in replacement for obsolete components in long term programs.

#### **Ordering Information**

The following part suffixes apply:

No suffix - MIL-STD-883 /2010B Visual Inspection

For High Reliability versions of this product please see

54ALS93

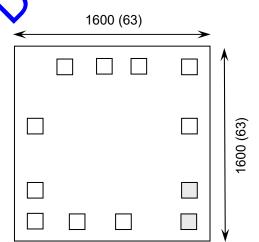

#### Die Dimensions in µm (mils)

#### Supply Formats:

- Defaut Die in Waffle Pack (100 per tray capacity)

- Sawn Wafer on Tape On request

- Unsawn Wafer On request

- Die Thickness <> 350µm(14 Mils) On request

- Assembled into Ceramic Package On request

#### **Mechanical Specification**

| Die Size (Unsawn)      | 1600 x 1600<br>63 x 63     | µm<br>mils |  |

|------------------------|----------------------------|------------|--|

| Minimum Bond Pad Size  | 130 x 130<br>5.12 x 5.12   | µm<br>mils |  |

| Die Thickness          | 350 (±20)<br>13.78 (±0.79) | μm<br>mils |  |

| Top Metal Composition  | Al 1%Si 1.1μ               | m          |  |

| Back Metal Composition | N/A – Bare Si              |            |  |

#### Rev 1.1 28/08/21

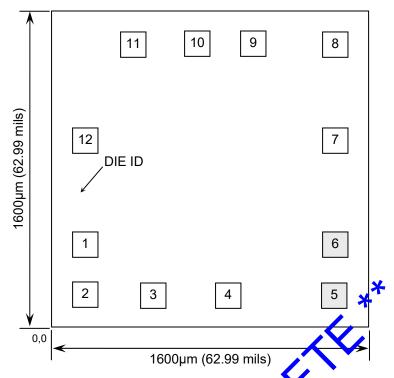

#### Pad Layout and Functions

|     |                   |           | $\leftarrow$ |

|-----|-------------------|-----------|--------------|

| PAD | FUNCTION          | COORDIN   | ATES (mm)    |

| FAD | FUNCTION          | Х         | Y            |

| 1   | CK <sub>B</sub>   | 0.100     | 0.360        |

| 2   | R0 <sub>(1)</sub> | 0.100     | 0.100        |

| 3   | R0 <sub>(2)</sub> | 0.450     | 0.100        |

| 4   | Vo                | 0.830     | 0.100        |

| 5   | NO                | 1.370     | 0.100        |

| 6   | NC                | 1.370     | 0.360        |

| _TC | Q <sub>C</sub>    | 1.370     | 0.880        |

| 2   | Q <sub>B</sub>    | 1.370     | 1.370        |

| Э   | GND               | 0.960     | 1.370        |

| 10  | $Q_D$             | 0.670     | 1.370        |

| 11  | Q <sub>A</sub>    | 0.350     | 1.370        |

| 12  | CK <sub>A</sub>   | 0.100     | 0.880        |

|     | CONNECT CHI       | P BACK TO | GND          |

#### Logic Diagram

#### **Truth Table**

| COUNT                                           | OUTPUT         |                |                |       |  |  |

|-------------------------------------------------|----------------|----------------|----------------|-------|--|--|

| COOM                                            | Q <sub>A</sub> | Q <sub>B</sub> | Q <sub>C</sub> | $Q_D$ |  |  |

| 0                                               | L              | L              | L              | L     |  |  |

| 1                                               | H              | L              | L              | L     |  |  |

| 2                                               | L              | H              | L              | L     |  |  |

| 3                                               | H              | H              | L              | L     |  |  |

| 4                                               | L              | L              | H              | L     |  |  |

| 5                                               | Н              | L              | H              | L     |  |  |

| 6                                               | L              | H              | H              | L     |  |  |

| 7                                               | H              | H              | H              | L     |  |  |

| 8                                               | L              | L              | L              | Н     |  |  |

| 9                                               | Н              | L              | L              | Н     |  |  |

| 10                                              | L              | H              | L              | Н     |  |  |

| 11                                              | Н              | H              | L              | Н     |  |  |

| 12                                              | L              | L              | H              | Н     |  |  |

| 13                                              | Н              | L              | H              | Н     |  |  |

| 14                                              | L              | H              | H              | Н     |  |  |

| 15                                              | Н              | Н              | Н              | Н     |  |  |

| NOTE: OUTPUT QA IS CONNECTED TO INPUT CKB       |                |                |                |       |  |  |

| H = HIGH Voltage Level<br>L = LOW Voltage Level |                |                |                |       |  |  |

#### Mode Selection

| <b>X</b> RESET    | INPUT             | OUTPUT |       |         |       |  |

|-------------------|-------------------|--------|-------|---------|-------|--|

| R0 <sub>(1)</sub> | R0 <sub>(2)</sub> | $Q_A$  | $Q_B$ | $Q_{C}$ | $Q_D$ |  |

| Н                 | Н                 | L      | L     | L       | L     |  |

| L                 | Н                 | COUNT  |       |         |       |  |

| Н                 | L                 | COUNT  |       |         |       |  |

| L                 | L                 | COUNT  |       |         |       |  |

Rev 1.1 28/08/21

## Absolute Maximum Ratings<sup>1</sup>

| PARAMETER                             | SYMBOL           | VALUE      | UNIT |

|---------------------------------------|------------------|------------|------|

| DC Supply Voltage (Referenced to GND) | V <sub>CC</sub>  | 7.0        | V    |

| DC Input Voltage (Referenced to GND)  | V <sub>IN</sub>  | 7.0        |      |

| Storage Temperature Range             | T <sub>STG</sub> | -65 to 150 | ~    |

<sup>1.</sup> Operation above the absolute maximum rating may cause device failure. Operation at the absolute maximum ratings, for extended periods, may reduce device reliability.

#### **Recommended Operating Conditions**

| 1 5                                |                 |       |      |       |  |  |  |

|------------------------------------|-----------------|-------|------|-------|--|--|--|

| PARAMETER                          | SYMBOL          | MIN   | MAX  | STIND |  |  |  |

| Supply Voltage (Referenced to GND) | V <sub>CC</sub> | 4.75  | 5.25 |       |  |  |  |

| High-Level Input Voltage           | V <sub>IH</sub> | 2     | ~    | V     |  |  |  |

| Low-Level Input Voltage            | V <sub>IL</sub> | -     | 0.8  | V     |  |  |  |

| High-Level Output Current          | I <sub>OH</sub> | -     | -0.4 | mA    |  |  |  |

| Low-Level Output Current           | I <sub>OL</sub> | -     | 8    | mA    |  |  |  |

| Operating Temperature Range        | T <sub>J</sub>  | -40 🥕 | +85  | °C    |  |  |  |

| Operating Temperature Range        | T <sub>J</sub>  | -40   | +85  | °C    |  |  |  |

## DC Electrical Characteristics Voltage's referenced to GND, T<sub>J</sub> = -40°C to 85°C unless otherwise specified

| PARAMETER                           | SYMBOL CONDITIONS | LIMITS                                        |                    |       | UNITS |       |

|-------------------------------------|-------------------|-----------------------------------------------|--------------------|-------|-------|-------|

| FARAWILTER                          | STWIDOL           | CONDITIONS                                    | MIN                | TYP   | MAX   | ONITS |

| Minimum High-Level<br>Input Voltage | V <sub>IH</sub>   | 0                                             | 2                  | -     | -     | V     |

| Maximum Low-Level<br>Input Voltage  | V <sub>IL</sub>   | -                                             | -                  | -     | 0.8   | V     |

| Input Clamp Diode<br>Voltage        |                   | $V_{CC} = 4.5V$<br>$I_{IN} = -18mA$           | -                  | -0.65 | -1.5  | V     |

| Output Voltage High                 | V <sub>OH</sub>   | $V_{CC} = 4.5V, I_{OH} = -0.4mA$              | V <sub>CC</sub> -2 | -     | -     | V     |

| Output Voltage Lw                   | V <sub>OL</sub>   | V <sub>CC</sub> = 4.5V, I <sub>OL</sub> = 4mA | -                  | 0.25  | 0.4   | V     |

| odipat Volido 24.                   |                   | $V_{CC} = 4.5V, I_{OL} = 8mA$                 | -                  | 0.35  | 0.5   |       |

| Inp High Current                    | ı                 | $V_{CC} = 5.5V, V_{IN} = 2.7V$                | -                  | -     | 20    | μA    |

| inpat night Current                 | I <sub>IH</sub>   | $V_{CC} = 5.5V, V_{IN} = 7.0V$                | -                  | -     | 0.1   | mA    |

| Input Low Current                   | I <sub>IL</sub>   | $V_{CC} = 5.5V, V_{IL} = 0.4V$                | -                  | -     | -0.1  | mA    |

| Short Circuit Current <sup>2</sup>  | I <sub>os</sub>   | $V_{CC} = 5.5V, V_{OUT} = 2.25V$              | -30                | -     | -112  | mA    |

| Supply Current                      | I <sub>CC</sub>   | V <sub>CC</sub> = 5.5V                        | -                  | -     | 13    | mA    |

<sup>2.</sup> Not more than one output should be shorted at a time, nor for more than 1 second.

## AC Electrical Characteristics $^4$ V<sub>CC</sub> = 5V, T<sub>J</sub> = -40°C to 85°C unless otherwise specified

Rev 1.1 28/08/21

| PARAMETER                                 | SYMBOL CONDITIONS               |                                        | LIMITS      |              |     | DNITS |

|-------------------------------------------|---------------------------------|----------------------------------------|-------------|--------------|-----|-------|

| TANAMETER                                 | OTHIBOL                         |                                        | MIN         | TYP          | MAX |       |

| Input Clock<br>Frequency, CK <sub>A</sub> | f <sub>max</sub>                |                                        | 32          | -            | -   | MHz   |

| Input Clock<br>Frequency, CK <sub>B</sub> | max                             | $C_L = 50 pF, R_L = 510 \Omega$        | 16          | -            |     | MHz   |

| Fall, Rising Edge                         | t <sub>f</sub> , t <sub>r</sub> |                                        | -           | -            | 2   | ns    |

| Propagation Delay, $CK_A$ to $Q_A$        | t <sub>PLH</sub>                | $C_L = 50 pF, R_L = 510 \Omega$        | -           | 4            | 16  | ns    |

| Propagation Delay, $CK_A$ to $Q_A$        | t <sub>PHL</sub>                | $C_L = 50 pF, R_L = 510 \Omega$        | -           | ~ <u>O</u> ` | 18  | 113   |

| Propagation Delay, $CK_A$ to $Q_D$        | t <sub>PLH</sub>                | $C_L = 50 pF, R_L = 510 \Omega$        | -, <b>C</b> | <b>9</b> .   | 70  | ns    |

| Propagation Delay, $CK_A$ to $Q_D$        | t <sub>PHL</sub>                | $C_L = 50 pF, R_L = 510 \Omega$        |             | -            | 70  | ns    |

| Propagation Delay, $CK_B$ to $Q_B$        | t <sub>PLH</sub>                | $C_L = 50 pF, R_L = 510 \Omega$        | -           | -            | 16  | ns    |

| Propagation Delay, $CK_B$ to $Q_B$        | t <sub>PHL</sub>                | $C_L = 50 \text{pF}, R_L = 510 \Omega$ | -           | -            | 21  | ns    |

| Propagation Delay, $CK_B$ to $Q_C$        | t <sub>PLH</sub>                | $C_L = 50 pF, R_L = 510 \Omega$        | -           | -            | 32  | ns    |

| Propagation Delay, $CK_B$ to $Q_C$        | t <sub>PHL</sub>                | $C_L = 50 pF, R_L = 510 \Omega$        | -           | -            | 35  | ns    |

| Propagation Delay, $CK_B$ to $Q_D$        | t <sub>PLH</sub>                | $_{L}$ = 50pF, R <sub>L</sub> = 510Ω   | -           | -            | 51  | ns    |

| Propagation Delay, $CK_B$ to $Q_D$        | PHL                             | $C_L = 50 pF, R_L = 510 \Omega$        | -           | -            | 51  | ns    |

| Propagation Delay,<br>R0 to any output    | t <sub>PHL</sub>                | $C_L = 50 pF, R_L = 510 \Omega$        | -           | -            | 32  | ns    |

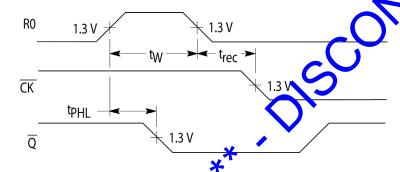

# Timing Requirements<sup>4</sup> V<sub>CC</sub> = 5V, T<sub>J</sub> = -40°C to 85°C unless otherwise specified

| PARAMETER                   | SYMBOL           | CONDITIONS                      |     | LIMITS |     | UNITS                                     |

|-----------------------------|------------------|---------------------------------|-----|--------|-----|-------------------------------------------|

| *                           | O'IIIBOL         |                                 | MIN | TYP    | MAX | J. G. |

| CK <sub>A</sub> Pulse Width |                  | $C_L = 50pF, R_L = 510\Omega$   | 15  | -      | -   | ns                                        |

| CK <sub>B</sub> Pulse Width | t <sub>W</sub>   |                                 | 30  | -      | -   | ns                                        |

| R0 Pulse Width              |                  |                                 | 15  | -      | -   | ns                                        |

| Recovery Time,<br>R0 to CK  | t <sub>REC</sub> | $C_L = 50 pF, R_L = 510 \Omega$ | 25  | -      | -   | ns                                        |

<sup>4.</sup> Not production tested in die form, characterized by chip design.

Rev 1.1 28/08/21

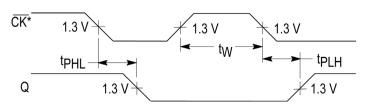

#### **Switching Waveforms**

\* The number of Clock Pulses required between the t<sub>PHL</sub> and t<sub>PLH</sub> measurements can be determined from the Truth Table

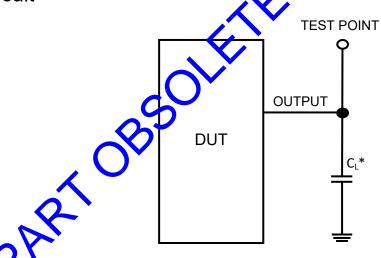

#### **Test Circuit**

\* Includes all probe and jig capacitance

DISCEAIMER: The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Silicon Supplies Ltd hereby disclaims any and all warranties and liabilities of any kind.

\* Includes all probe and jig capacitance LIFE SUPPORT POLICY: Silicon Supplies Ltd components may be used in life support devices or systems only with the express written approval of Silicon Supplies Ltd, if a failure of such components can reasonably be expected to cause the failure of that life support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.