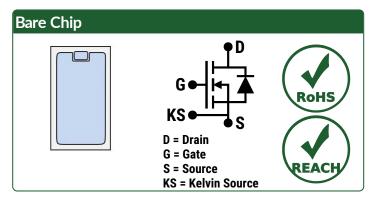

#### Silicon Carbide MOSFET N-Channel Enhancement Mode

For physical chip dimensions please contact engineering@diedevices.com

$\begin{array}{cccc} V_{DS} & = & 1700 \text{ V} \\ R_{DS(ON)(Typ.)} & = & 45 \text{ m}\Omega \\ I_{D(Tc} = 100^{\circ}\text{C)} & = & 40 \text{ A} \end{array}$

#### **Features**

- G3R™ Technology with +15 V Gate Drive

- Softer R<sub>DS(ON)</sub> v/s Temperature Dependency

- LoRing<sup>™</sup> Electromagnetically Optimized Design

- Smaller R<sub>G(INT)</sub> and Lower Q<sub>G</sub>

- Low Device Capacitances (Coss, Crss)

- Superior Cost-Performance Index

- Robust Body Diode with Low V<sub>F</sub> and Low Q<sub>RR</sub>

- Industry-Leading UIL & Short-Circuit Robustness

#### Advantages

- Compatible with Commercial Gate Drivers

- Low Conduction Losses at all Temperatures

- Reduced Ringing

- Faster and More Efficient Switching

- Lesser Switching Spikes and Lower Losses

- Better Power Density and System Efficiency

- Ease of Paralleling without Thermal Runaway

- Higher System Reliability

#### **Applications**

- Electric Vehicle Fast Charging

- Solar Inverters

- Traction Inverters

- Smart Grid and HVDC

- High Voltage DC-DC Converters

- Switched Mode Power Supply

- Wind Energy Converters

- Pulsed Power

| Absolute Maximum Ratings (At $T_C = 2$ |                                   | <u> </u>                                                  |            |      |        |

|----------------------------------------|-----------------------------------|-----------------------------------------------------------|------------|------|--------|

| Parameter                              | Symbol                            | Conditions                                                | Values     | Unit | Note   |

| Drain-Source Voltage                   | $V_{DS(max)}$                     | $V_{GS}$ = 0 V, $I_D$ = 100 $\mu A$                       | 1700       | V    |        |

| Gate-Source Voltage (Dynamic)          | V <sub>GS(max)</sub>              |                                                           | -10 / +20  | V    |        |

| Gate-Source Voltage (Static)           | V <sub>GS(op)</sub>               | Recommended Operation                                     | -5 / +15   | V    |        |

|                                        |                                   | $T_C = 25^{\circ}C$ , $V_{GS} = -5 / +15 V$               | 53         |      |        |

| Continuous Forward Current             | $I_{D}$                           | $T_C = 100$ °C, $V_{GS} = -5 / +15 V$                     | 40         | Α    |        |

|                                        |                                   | $T_C = 135^{\circ}C$ , $V_{GS} = -5 / +15 V$              | 32         |      |        |

| Pulsed Drain Current                   | I <sub>D(pulse)</sub>             | $t_P \le 3\mu s$ , D $\le 1\%$ , $V_{GS} = 15 V$ , Note 1 | 120        | Α    |        |

| Power Dissipation                      | PD                                | T <sub>c</sub> = 25°C                                     | 425        | W    | Note 2 |

| Non-Repetitive Avalanche Energy        | Eas                               | L = 3.9 mH, I <sub>AS</sub> = 17.5 A                      | 592        | mJ   |        |

| Operating and Storage Temperature      | T <sub>j</sub> , T <sub>stg</sub> |                                                           | -55 to 200 | °C   |        |

Note 1: Pulse Width t<sub>P</sub> Limited by T<sub>j(max)</sub>

#### Electrical Characteristics (At T<sub>C</sub> = 25°C Unless Otherwise Stated)

| Parameter                                     | Symbol               | Conditions -                                                                                                   | Values |      |      | 11. 11   |          |

|-----------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------|--------|------|------|----------|----------|

|                                               |                      |                                                                                                                | Min.   | Тур. | Max. | - Unit   | Note     |

| Drain-Source Breakdown Voltage                | $V_{\text{DSS}}$     | $V_{GS} = 0 \text{ V, } I_{D} = 100  \mu\text{A}$                                                              | 1700   |      |      | V        |          |

| Zero Gate Voltage Drain Current               | I <sub>DSS</sub>     | $V_{DS}$ = 1700 V, $V_{GS}$ = 0 V                                                                              |        | 1    |      | μΑ       |          |

| Gate Source Leakage Current                   | I <sub>GSS</sub>     | $V_{DS} = 0 \text{ V, } V_{GS} = 20 \text{ V}$                                                                 |        |      | 100  | nA       |          |

|                                               |                      | $V_{DS} = 0 \text{ V, } V_{GS} = -10 \text{ V}$                                                                |        |      | -100 | 11/4     |          |

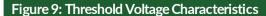

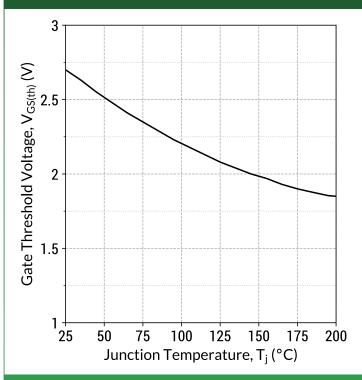

| Gate Threshold Voltage                        | V <sub>GS(th)</sub>  | $V_{DS} = V_{GS}$ , $I_D = 30.0 \text{ mA}$                                                                    | 1.8    | 2.70 |      | V        | Fig. 9   |

|                                               |                      | $V_{DS} = V_{GS}$ , $I_D = 30.0$ mA, $T_j = 200$ °C                                                            |        | 1.85 |      | •        |          |

| Transconductance                              | <b>G</b> fs          | $V_{DS} = 10 \text{ V}, I_D = 35 \text{ A}$                                                                    |        | 16.8 |      | S        | Fig. 4   |

| Tanoonauotanoo                                | <b>3</b> 13          | $V_{DS} = 10 \text{ V, } I_D = 35 \text{ A, } T_j = 200^{\circ}\text{C}$                                       |        | 16.6 |      |          |          |

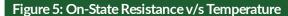

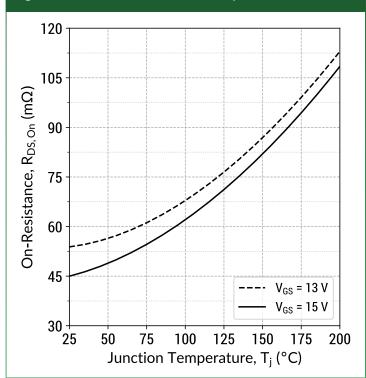

| Drain-Source On-State Resistance              | R <sub>DS(ON)</sub>  | $V_{GS} = 15 \text{ V}, I_D = 35 \text{ A}$                                                                    |        | 45   | 62   | 62<br>mΩ | Fig. 5-8 |

|                                               |                      | $V_{GS}$ = 15 V, $I_D$ = 35 A, $T_j$ = 200°C                                                                   |        | 108  |      |          |          |

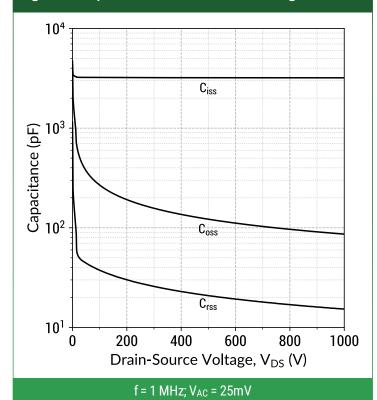

| Input Capacitance                             | Ciss                 |                                                                                                                |        | 3199 |      | _        | Fig. 11  |

| Output Capacitance                            | Coss                 |                                                                                                                |        | 86   |      | pF       |          |

| Reverse Transfer Capacitance                  | Crss                 |                                                                                                                |        | 15.3 |      |          |          |

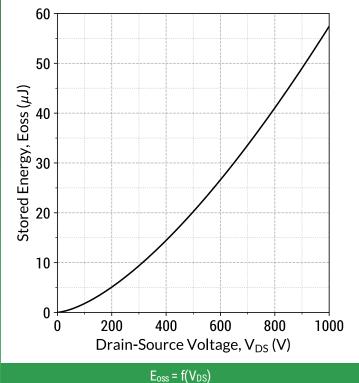

| Coss Stored Energy                            | Eoss                 |                                                                                                                |        | 57   |      | μJ       | Fig. 12  |

| C <sub>oss</sub> Stored Charge                | Qoss                 | f = 1 MHz, V <sub>AC</sub> = 25mV                                                                              |        | 172  |      | nC       |          |

| Effective Output Capacitance (Energy Related) | $C_{o(\text{er})}$   |                                                                                                                |        | 114  |      | pF       | Note 3   |

| Effective Output Capacitance (Time Related)   | $C_{o(tr)}$          |                                                                                                                |        | 172  |      | μг       | Note 3   |

| Gate-Source Charge                            | Qgs                  | V <sub>DS</sub> = 1000 V, V <sub>GS</sub> = -5 / +15 V<br>I <sub>D</sub> = 35 A                                |        | 33   |      |          | Fig. 10  |

| Gate-Drain Charge                             | Qgd                  |                                                                                                                |        | 37   |      | nC       |          |

| Total Gate Charge                             | Qg                   | Per IEC607478-4                                                                                                |        | 106  |      |          |          |

| Internal Gate Resistance                      | R <sub>G</sub> (int) | $f = 1 MHz$ , $V_{AC} = 25 mV$                                                                                 |        | 1.3  |      | Ω        |          |

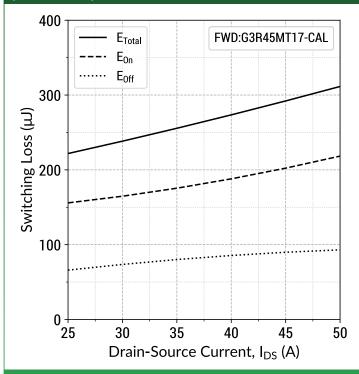

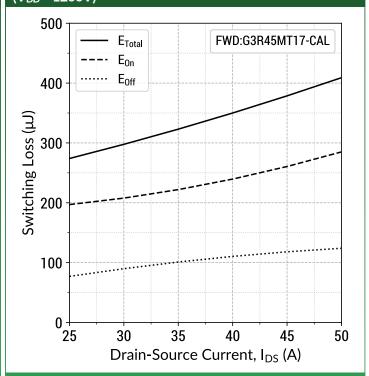

| Turn-On Switching Energy<br>(Body Diode)      | E <sub>On</sub>      | $T_i = 25$ °C; $V_{GS} = -5/+15V$ ; $R_{G(ext)} = 1 \Omega$ , $I_D =$                                          |        | 222  |      | 1        | Fig. 18  |

| Turn-Off Switching Energy<br>(Body Diode)     | E <sub>Off</sub>     | 35 A; V <sub>DD</sub> = 1200 V                                                                                 |        | 100  |      | μJ       |          |

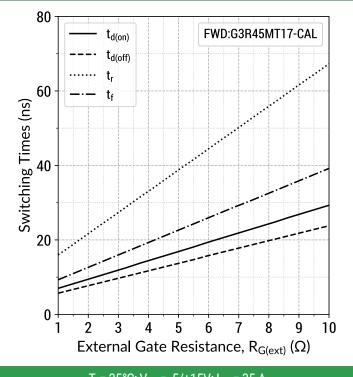

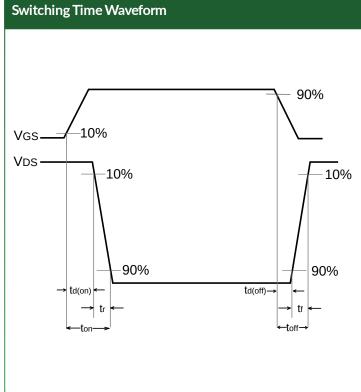

| Turn-On Delay Time                            | t <sub>d(on)</sub>   |                                                                                                                |        | 7    |      |          | Fig. 20  |

| Rise Time                                     | t <sub>r</sub>       | $V_{DD} = 1200 \text{ V, } V_{GS} = -5/+15 \text{ V}$                                                          |        | 16   |      |          |          |

| Turn-Off Delay Time                           | t <sub>d(off)</sub>  | - R <sub>G(ext)</sub> = 1 Ω, I <sub>D</sub> = 35 A $-$ Timing relative to V <sub>DS</sub> , Resistive load $-$ |        | 6    |      | ns       |          |

| Fall Time                                     | tf                   | — Tilling relative to $v_{DS}$ , resistive load -                                                              |        | 10   |      |          |          |

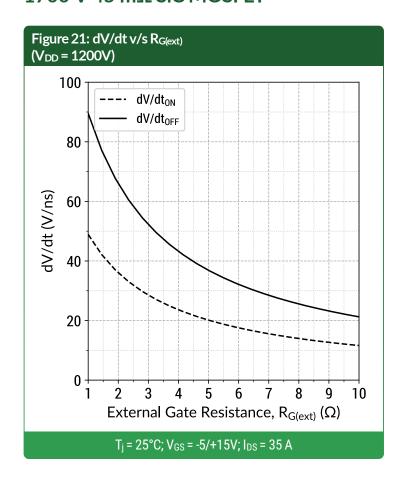

<sup>\*</sup>The chip technology was characterized up to 200 V/ns. The measured dV/dt was limited by measurement test setup and package.

Note 2: Assuming Rth<sub>JC(max)</sub> = 0.41 °C/W

Note 3:  $C_{O(er)}$ , a lumped capacitance that gives same stored energy as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 1000V.  $C_{O(tr)}$ , a lumped capacitance that gives same charging times as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 1000V.

| Reverse Diode Characteristics    |                  |                                                                                                                      |        |      |      |       |            |

|----------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------|--------|------|------|-------|------------|

| Parameter                        | Symbol           | Conditions                                                                                                           | Values |      |      | Unit  | Note       |

|                                  |                  |                                                                                                                      | Min.   | Тур. | Max. | Ullit | Note       |

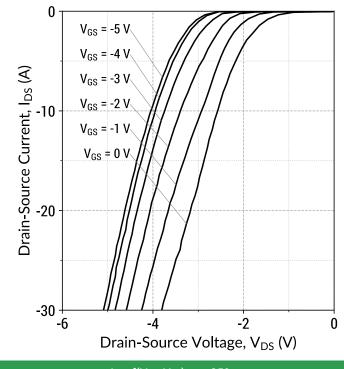

| Diode Forward Voltage            | V <sub>SD</sub>  | $V_{GS} = -5 \text{ V, } I_{SD} = 17 \text{ A}$                                                                      |        | 4.5  |      | V     | Fig. 10.14 |

|                                  |                  | $V_{GS}$ = -5 V, $I_{SD}$ = 17 A, $T_j$ = 200°C                                                                      |        | 4.3  |      | V FI  | Fig. 13-14 |

| Continuous Diode Forward Current | Is               | $V_{GS} = -5 \text{ V, } T_{c} = 100^{\circ}\text{C}$                                                                | 41     |      |      | Α     |            |

| Diode Pulse Current              | Is(pulse)        | V <sub>GS</sub> = -5 V, Note 1                                                                                       |        | 164  |      | Α     |            |

| Reverse Recovery Time            | t <sub>rr</sub>  | V <sub>GS</sub> = -5 V, I <sub>SD</sub> = 35 A, V <sub>R</sub> = 1200 V<br>dif/dt = 2200 A/μs, T <sub>j</sub> = 25°C |        | 31   |      | ns    |            |

| Reverse Recovery Charge          | Qrr              |                                                                                                                      |        | 305  |      | nC    |            |

| Peak Reverse Recovery Current    | I <sub>rrm</sub> |                                                                                                                      |        | 8    |      | Α     |            |

| Reverse Recovery Time            | t <sub>rr</sub>  | $V_{GS}$ = -5 V, $I_{SD}$ = 35 A, $V_R$ = 1200 V dif/dt = 2200 A/ $\mu$ s, $T_j$ = 200°C                             |        | 56   |      | ns    |            |

| Reverse Recovery Charge          | Qrr              |                                                                                                                      |        | 1174 |      | nC    |            |

| Peak Reverse Recovery Current    | I <sub>rrm</sub> |                                                                                                                      |        | 18   |      | Α     |            |

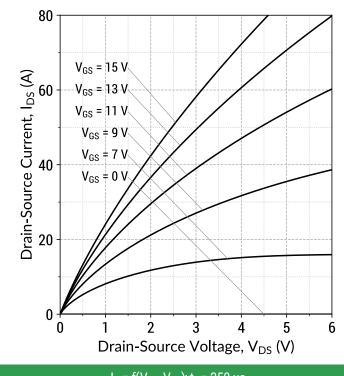

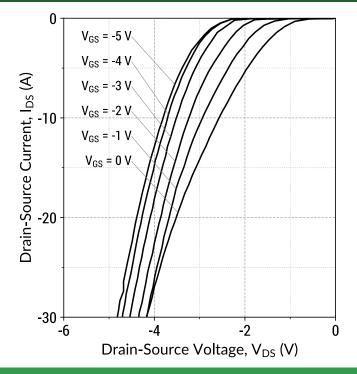

Figure 1: Output Characteristics (T<sub>i</sub> = 25°C)

$I_D = f(V_{DS}, V_{GS}); t_P = 250 \ \mu s$

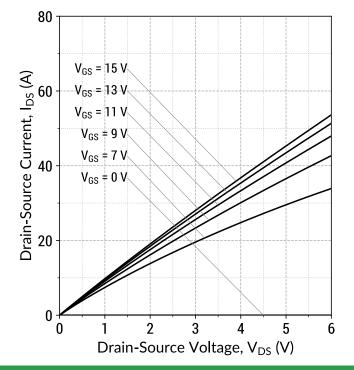

Figure 2: Output Characteristics (T<sub>i</sub> = 200°C)

$I_D = f(V_{DS}, V_{GS}); t_P = 250 \mu s$

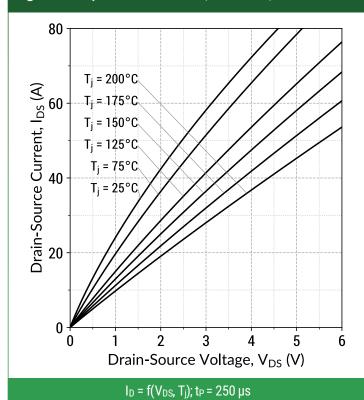

Figure 3: Output Characteristics (V<sub>GS</sub> = 15 V)

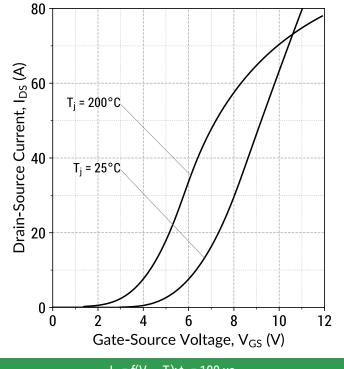

Figure 4: Transfer Characteristics (V<sub>DS</sub> = 10 V)

$I_D = f(V_{GS}, T_j); t_P = 100 \ \mu s$

$R_{DS(ON)} = f(T_j, V_{GS}); t_P = 250 \mu s; I_D = 35 A$

Figure 6: On-State Resistance v/s Drain Current

$R_{DS(ON)} = f(T_j, I_D); t_P = 250 \mu s; V_{GS} = 15 V$

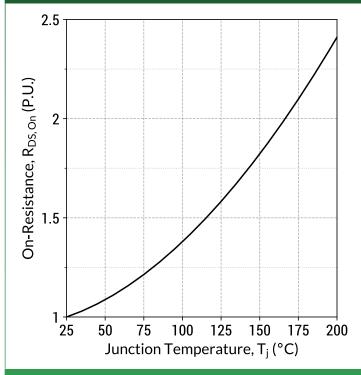

Figure 7: Normalized On-State Resistance v/s Temperature

$R_{DS(ON)} = f(T_i); t_P = 250 \mu s; I_D = 35 A; V_{GS} = 15 V$

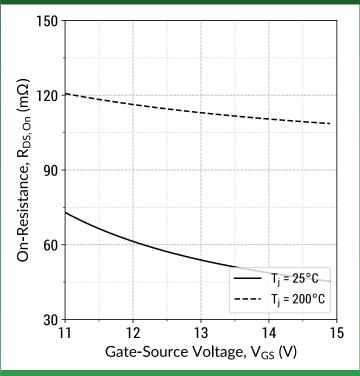

Figure 8: On-State Resistance v/s Gate Voltage

$R_{DS(ON)} = f(T_j, V_{GS}); t_P = 250 \mu s; I_D = 35 A$

$V_{GS(th)} = f(T_j); V_{DS} = V_{GS}; I_D = 30.0 \text{ mA}$

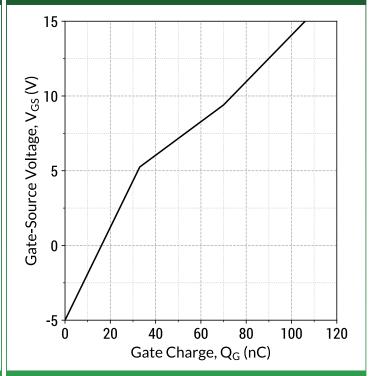

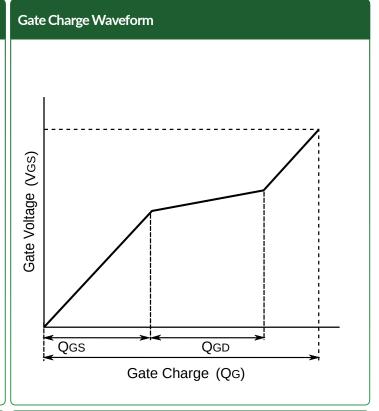

Figure 10: Gate Charge Characteristics

$I_D = 35 \text{ A}$ ;  $V_{DS} = 1000 \text{ V}$ ;  $T_c = 25 ^{\circ}\text{C}$

Figure 11: Capacitance v/s Drain-Source Voltage

Figure 12: Output Capacitor Stored Energy

Figure 13: Body Diode Characteristics (T<sub>i</sub> = 25°C)

$I_D = f(V_{DS}, V_{GS}); t_P = 250 \,\mu s$

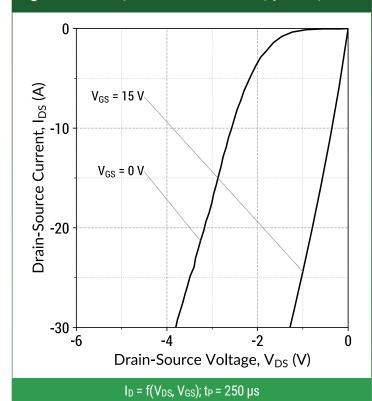

Figure 14: Body Diode Characteristics (T<sub>j</sub> = 200°C)

$I_D = f(V_{DS}, V_{GS}); t_P = 250 \mu s$

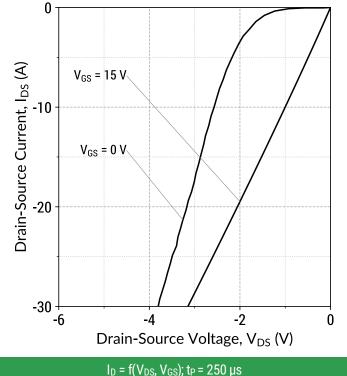

Figure 15: Third Quadrant Characteristics (T<sub>i</sub> = 25°C)

Figure 16: Third Quadrant Characteristics (T<sub>j</sub> = 200°C)

Figure 17: Resistive Switching Energy v/s Drain Current  $(V_{DD} = 1000V)$

$T_j$  = 25°C;  $V_{GS}$  = -5/+15V;  $R_{G(ext)}$  = 1  $\Omega$

Figure 18: Resistive Switching Energy v/s Drain Current (V<sub>DD</sub> = 1200V)

$T_i = 25$ °C;  $V_{GS} = -5/+15V$ ;  $R_{G(ext)} = 1 \Omega$

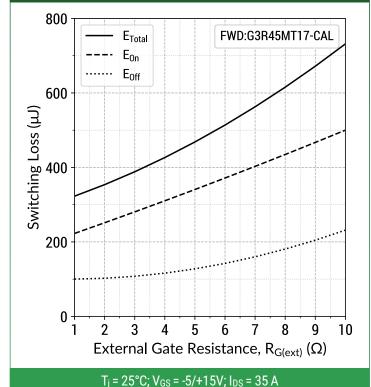

Figure 19: Resistive Switching Energy v/s  $R_{G(ext)}$  ( $V_{DD} = 1200V$ )

Figure 20: Switching Time v/s  $R_{G(ext)}$  ( $V_{DD} = 1200V$ )

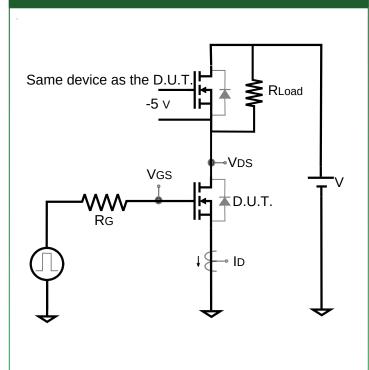

## Gate Charge Circuit VDS Vgs D.U.T RLoad $V_{DD}$ o ↓ ID

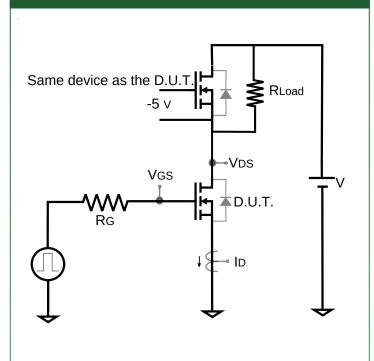

## **Switching Time Circuit**

IG(cont)

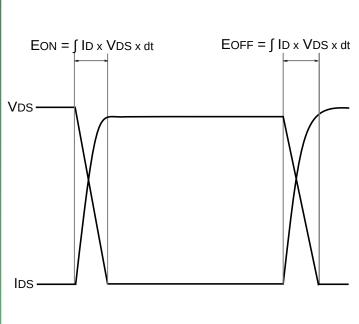

## Switching Energy Circuit

## Switching Energy Waveform

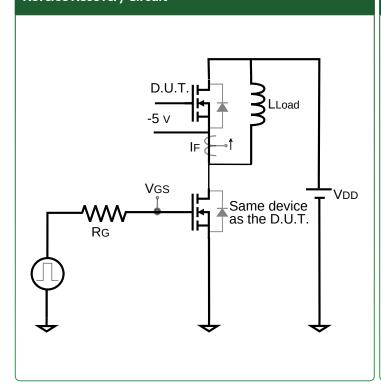

### Reverse Recovery Circuit

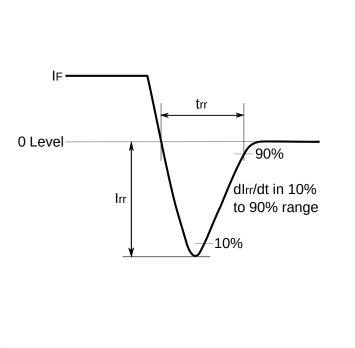

### Reverse Recovery Waveform

#### **Mechanical Parameters**

This information is confidential, please contact sales@genesicsemi.com to learn more.

### **Chip Dimensions**

This information is confidential, please contact <a href="mailto:sales@genesicsemi.com">sales@genesicsemi.com</a> to learn more.

#### NOTE

- 1. CONTROLLED DIMENSION IS MILLIMETER.

- 2. DIMENSIONS DO NOT INCLUDE END FLASH, MOLD FLASH, MATERIAL PROTRUSIONS.

#### Compliance

#### **RoHS Compliance**

The levels of RoHS restricted materials in this product are below the maximum concentration values (also referred to as the threshold limits) permitted for such substances, or are used in an exempted application, in accordance with EU Directive 2011/65/EC (RoHS 2), as adopted by EU member states on January 2, 2013 and amended on March 31, 2015 by EU Directive 2015/863. RoHS Declarations for this product can be obtained from your GeneSiC representative.

#### **REACH Compliance**

REACH substances of high concern (SVHCs) information is available for this product. Since the European Chemical Agency (ECHA) has published notice of their intent to frequently revise the SVHC listing for the foreseeable future, please contact a GeneSiC representative to insure you get the most up-to-date REACH SVHC Declaration. REACH banned substance information (REACH Article 67) is also available upon request.

#### Disclaimer

GeneSiC Semiconductor, Inc. reserves right to make changes to the product specifications and data in this document without notice. GeneSiC disclaims all and any warranty and liability arising out of use or application of any product. No license, express or implied to any intellectual property rights is granted by this document.

Unless otherwise expressly indicated, GeneSiC products are not designed, tested or authorized for use in life-saving, medical, aircraft navigation, communication, air traffic control and weapons systems, nor in applications where their failure may result in death, personal injury and/or property damage.

#### **Related Links**

SPICE Models: https://www.genesicsemi.com/sic-mosfet/G3R45MT17-CAL/G3R45MT17-CAL\_SPICE.zip

PLECS Models: https://www.genesicsemi.com/sic-mosfet/G3R45MT17-CAL/G3R45MT17-CAL\_PLECS.zip

CAD Models: https://www.genesicsemi.com/sic-mosfet/G3R45MT17-CAL/G3R45MT17-CAL\_3D.zip

Gate Driver Reference: https://www.genesicsemi.com/technical-support

Evaluation Boards: https://www.genesicsemi.com/technical-support

Reliability: https://www.genesicsemi.com/reliability

Compliance: https://www.genesicsemi.com/compliance

Quality Manual: https://www.genesicsemi.com/guality

#### **Revision History**

• Rev 21/Jun: Updated switching time and switching energy data

· Supersedes: Rev 20/Jun, Rev 20/Sep, Rev 21/Feb

www.genesicsemi.com/sic-mosfet/